| - N      |  |  |  |  |  |

|----------|--|--|--|--|--|

| Reg. No. |  |  |  |  |  |

|          |  |  |  |  |  |

## MANIPAL INSTITUTE OF TECHNOLOGY

(A Constituent Institute of Manipal University) Manipal – 576 104

## IV SEMESTER B.Tech (BME) DEGREE END SEM EXAMINATIONS, MAY 2016

## **SUBJECT: DIGITAL ELECTRONICS (BME 204)**

(REVISED CREDIT SYSTEM)

Thursday, 5th May 2016: 2.00 p.m.- 5.00 pm

**TIME: 3 HOURS**

MAX. MARKS: 100

Instructions to Candidates:

| 1.<br>2. | Answer any FIVE full questions.  Draw labeled diagram wherever necessary |                                                                                                                                                                                                  |    |  |  |  |

|----------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 1        | (0)                                                                      | Poolize on Ev. OP gets using only minimum number of NOP gets                                                                                                                                     | 05 |  |  |  |

| 1.       | (a)                                                                      | Realize an Ex-OR gate using only minimum number of NOR gates.                                                                                                                                    |    |  |  |  |

|          | (b)                                                                      | Give the truth table of a full adder. Realize the expression of sum and carry and draw the logic circuit using basic gates.                                                                      | 07 |  |  |  |

|          | (c)                                                                      | Find the SOP and POS of the following function.                                                                                                                                                  | 06 |  |  |  |

|          |                                                                          | $f(ABC) = A + \overline{B}C + B\overline{C}$                                                                                                                                                     |    |  |  |  |

|          | (d)                                                                      | Convert the following                                                                                                                                                                            | 02 |  |  |  |

|          |                                                                          | $(415)_8 = ()_2$                                                                                                                                                                                 |    |  |  |  |

|          |                                                                          | $(BC2)_{16} = ()_2$                                                                                                                                                                              |    |  |  |  |

| 2.       | (a)                                                                      | Realize and draw logic circuit of 1×8 line de-multiplexer.                                                                                                                                       | 06 |  |  |  |

|          | (b)                                                                      | Implement the following Boolean function using $8 \times 1$ line multiplexer with A as input line and BCD as select lines. $f(A, B, C, D) = \sum_{i=0}^{\infty} 0.1, 3.5, 7.8, 9.10, 12, 14, 15$ | 06 |  |  |  |

|          | (c)                                                                      | Write a note on,                                                                                                                                                                                 | 08 |  |  |  |

|          | ( )                                                                      | (i) ROM (ii) Parity generator.                                                                                                                                                                   |    |  |  |  |

| 3.       | (a)                                                                      | Draw the logic circuit of JK flip flop using only NAND gates. Explain its operation with the truth table.                                                                                        | 06 |  |  |  |

|          | (b)                                                                      | Draw the circuit of a Mod-10 asynchronous counter using JK FF and explain its operation with timing diagram.                                                                                     | 08 |  |  |  |

|          | (c)                                                                      | Draw the circuit of 3 input TTL NAND gate and explain its operation.                                                                                                                             | 06 |  |  |  |

| 4.       | (a)                                                                      | Design and draw a Mod-8 synchronous counter using D flip flops. Explain its operation with waveforms.                                                                                            | 08 |  |  |  |

|          | (b)                                                                      | Draw the circuit of a Mod-10 Johnson counter. Explain its operation and find the legal and illegal count sequences.                                                                              | 08 |  |  |  |

|          | (c)                                                                      | Realize and draw the circuit of one bit comparator and explain.                                                                                                                                  | 04 |  |  |  |

BME 204 Page 1 of 2

- 5. (a) A square wave whose peak to peak value is 10 volt extends ±5 volts with respect to ground. The duration of the positive section is 0.1msec and of the negative section is 0.2msec. If this waveform is impressed upon an RC high pass circuit whose time constant is 0.2msec, what are the steady state maximum and minimum values of the output wave form?

- (b) Derive the expression of output if a ramp waveform  $V_i = \alpha t$  is applied to a high pass RC circuit, whose time constant is RC, where  $\alpha$  is the slope of the ramp wave.

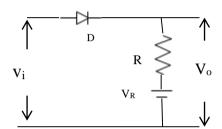

- (c) (i) The input voltage Vi is a sinusoidal waveform, is applied to the clipping circuit shown in fig.Q5c. Sketch the output voltage  $V_0$  and draw the transfer characteristics  $V_i$   $V_s$   $V_o$ . Consider diode to be ideal.

- (ii) With the polarity of the diode interchanged, repeat part (i)

Fig.Q5c

- 6. (a) Draw the circuit of a mono-stable multi-vibrator circuit using transistors. Explain 10 its operation with waveforms and derive the relation of pulse width.

- (b) Draw the circuit of a fixed biased binary using silicon *npn* transistors.

For this circuit  $h_{FE,min} = 30$ . The junction saturation voltages are,

$$V_{CEsat} = 0.2 Volts$$

,  $V_{BEsat} = 0.8 Volts$ .

The circuit parameters are,

$V_{CC}=12 Volts$ ,  $V_{BB}=-3 volts$ ,  $R_1=5 K \Omega$ ,  $R_2=10 K \Omega$ ,  $R_C=1 K \Omega$ . Find the stable state voltages and currents.

BME 204 Page 2 of 2