## 5A. Write a structural Verilog code for 4 bit carry ripple adder (CRA) using 1-bit full adder module.

- Write the switch level Verilog HDL code for two-input CMOS NAND gate. 5B.

- 5C. Implement the following expression using Altera MAX FPGA having 3 wide AND OR array plane.  $F = AB\overline{C} + \overline{A}\overline{B} + \overline{B}C + \overline{A}\overline{D} + AB\overline{D}$

(5+3+2)

(5+3+2)

1A. Implement 3 bit binary- to-gray code converter using ACT1 series

2B. Implement following function using Xilinx XC 3000. How many CLBs and LUTs are required?

Explain the following terms: [i] channeled and channelless gate array [ii] Logic Synthesis

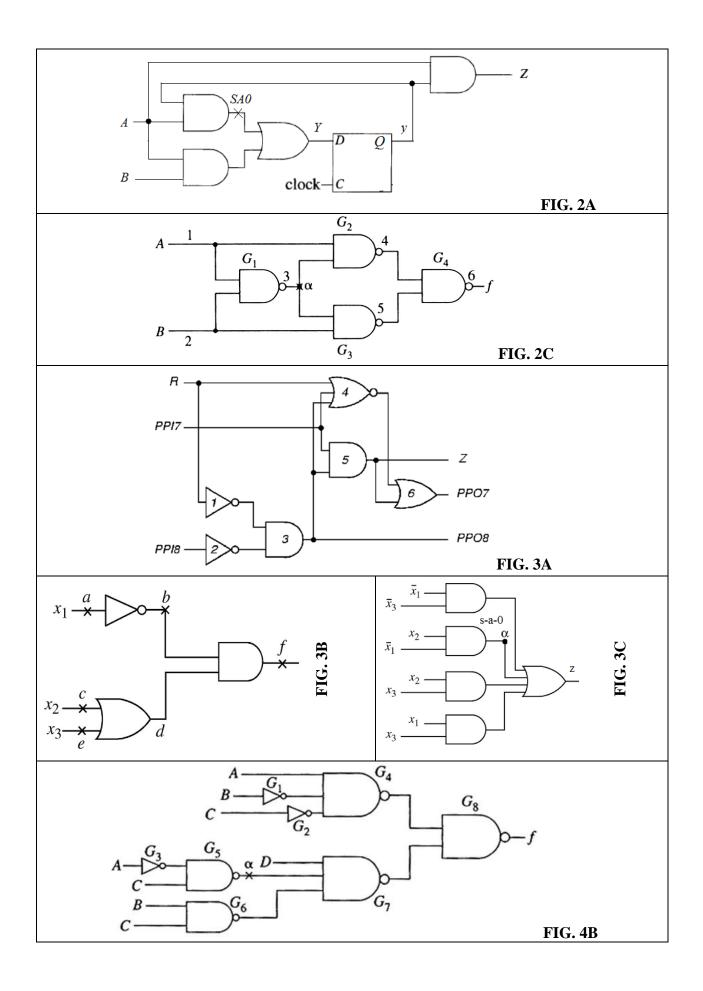

- 2C. Find the test vector for SA1 fault at node  $\alpha$  shown in **FIG. 2C** using D-Algorithm

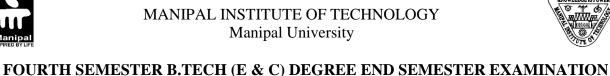

- 3A. Find combinational controllability and observability measures of all the nodes for the circuit in FIG. 3A.

- 3B. Obtain the minimal test vector set for the fault set {a0, b0, c0, d1, e0, f1} in the circuit of **FIG. 3B** using fault table method.

- 3C. How will you enhance the observability of node  $\alpha$  in the circuit of **FIG.3C**.

4A. Write a sequential Verilog code for 4-bit Carry Look Ahead (CLA) adder.

- 4B. Find the test vector to detect the fault SA1 at node  $\alpha$  for the circuit in **FIG. 4B** by path sensitization method.

- 4C. Give a data-flow Verilog model for 3-to-8 decoder with enable input and active high output.

2A. Find the test vector for SA0 fault shown in FIG. 2A using ITG

- $F(a, b, c, d, e) = a. b. c + a. \overline{b}. c + \overline{e} + d. e$

Reg. No.

MANIPAL INSTITUTE OF TECHNOLOGY Manipal University

**MAY/ JUNE 2016** SUBJECT: DIGITAL SYSTEM DESIGN USING VERILOG (ECE - 2204)

**TIME: 3 HOURS**

•

ECE -2204

1B.

Instructions to candidates

[iii] antifuse switch

1C. Compare ASIC and FPGA.

Answer ALL questions.

Missing data may be suitably assumed.

MAX. MARKS: 50

(5+3+2)

(5+3+2)

(5+3+2)