Reg. No.

**III SEMESTER B.TECH (ELECTRICAL & ELECTRONICS ENGINEERING)**

## END SEMESTER EXAMINATIONS NOV/ DEC 2016

## SUBJECT: ANALOG ELECTRONIC CIRCUITS [ELE 2105]

**REVISED CREDIT SYSTEM**

| Time:                       | 3 Hours Date:                                                                                                                                                                                                                                                  | 06 December 2016                                                                                                                                                                      | MAX. MAF                             | RKS: 50 |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|

| Instructions to Candidates: |                                                                                                                                                                                                                                                                |                                                                                                                                                                                       |                                      |         |

|                             | <ul> <li>Answer ALL the questions.</li> </ul>                                                                                                                                                                                                                  |                                                                                                                                                                                       |                                      |         |

|                             | <ul> <li>Missing data may be suitably as</li> </ul>                                                                                                                                                                                                            | sumed.                                                                                                                                                                                |                                      |         |

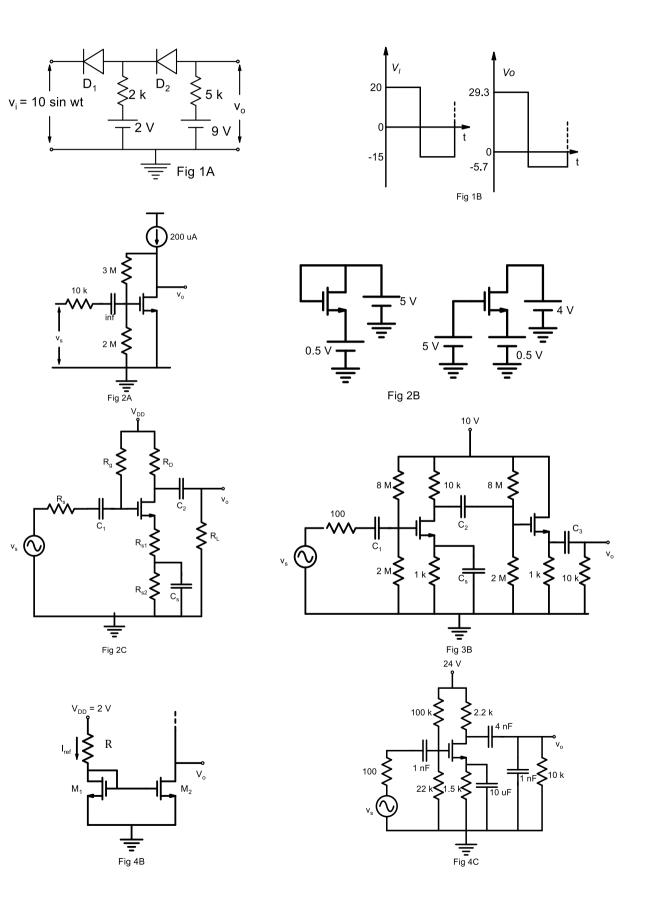

| 1A.                         | Plot the output waveform and tr Assume $V_D$ =0.3V.                                                                                                                                                                                                            | ansfer characteristics for the circuit shown                                                                                                                                          | in Fig. 1A.                          | (04)    |

| 1B.                         | Analyze the waveforms shown in Fig. 1B and obtain the suitable diode based circuit $V_D$ =0.7V.                                                                                                                                                                |                                                                                                                                                                                       | iit. Assume                          | (03)    |

| 1C.                         | a supply whose voltage varies be                                                                                                                                                                                                                               | yed to provide a constant output voltage of $V_L$ =<br>etween 11 V and 13.6 V. The load resistance<br>ng $I_{zmin}$ = 0.1 times $I_{zmax}$ , determine the power<br>esistor employed. | may vary                             | (03)    |

| 2A.                         | For the circuit shown in Fig. 2A, $\mu_n C_{ox}(W/L) = 2 \text{ mA}/V^2$ .                                                                                                                                                                                     | letermine the value of $V_{\text{GS}}$ , $V_{\text{DS}}$ and $g_{\text{m}}.$ Given $V$                                                                                                | $V_{\rm th} = 0.5  {\rm V}$ ,        | (04)    |

| 2B.                         | Determine the region of operation $V_{\rm th}$ = 0.4 V.                                                                                                                                                                                                        | of MOSFET in each of the circuit shown in Fig. 2                                                                                                                                      | B, Assume                            | (02)    |

| 2C.                         | For the circuit shown in Fig. 2C, ob                                                                                                                                                                                                                           | tain an expression for small signal voltage gain                                                                                                                                      | $\frac{V_o}{V_s}$ . Hence            |         |

|                             | draw the small signal model.                                                                                                                                                                                                                                   |                                                                                                                                                                                       |                                      | (04)    |

| 3A.                         | Find the bandwidth of three cascaded identical amplifiers, with each of them having 500 Hz as low cut off frequency and 25 kHz as upper cut off frequency. Also, draw the frequency response of cascaded amplifiers in comparison with single stage amplifier. |                                                                                                                                                                                       | (03)                                 |         |

| 3B.                         | Determine the small signal voltage shown in Fig.3B. Assume $g_{m1} = g_{m2}$                                                                                                                                                                                   | gain and output resistance of the cascaded amp = $1 \text{ mA/V}^2$ , $\kappa = 0$ .                                                                                                  | olifier                              | (05)    |

| 3C.                         | Find the transconductance and W/L=20, $I_{DSAT}$ =1.5mA.                                                                                                                                                                                                       | $V_{GS}$ of n channel MOSFET. Vth=0.6V. ( $\mu_n c_{os}$                                                                                                                              | e)=60µA/V,                           | (02)    |

| 4A.                         | frequency is 5 V/V. The parameter $V_{DD}$ = 1.8 V. In this circuit, if an $R_S$ =                                                                                                                                                                             | rce amplifier circuit, maximum voltage gain a<br>s are: $\mu_n C_{ox} = 100 \ \mu A/V^2$ , $V_{th} = 0.5 \ V$ , (W/L) = 10<br>= $R_D$ is added, find the voltage gains across $R_D$ a | ), $V_{GS} = 1 V$ ,<br>nd $R_S$ with |         |

|                             |                                                                                                                                                                                                                                                                | Ience comment on the nature of these gains obt                                                                                                                                        |                                      | (04)    |

| 4B.                         |                                                                                                                                                                                                                                                                | and resistance R in the circuit shown in Fig. 4B $M_1$ and $M_2$ as identical and $\mu_n C_{ox}$ =90 $\mu A/V^2$ , $V_{th}$                                                           |                                      | (03)    |

| 4C.                         | Determine the lower and upper cut                                                                                                                                                                                                                              | off frequencies for the circuit shown in Fig. 4C.                                                                                                                                     |                                      | (03)    |

| 5A.                         | With a neat circuit and diagram an transformer coupled class A power                                                                                                                                                                                           | nd necessary waveforms, obtain maximum effi<br>amplifier.                                                                                                                             | ciency of a                          | (03)    |

- 5B. For a class B amplifier providing a 18-V peak signal to a 16  $\Omega$  load and a power supply of  $V_{DD}=|V_{SS}|=24$  V, determine the input power, output power and circuit efficiency. (03)

- For the MOS Differential pair derive expression for CMRR. Also explain the importance of 5C. (04) Active load with the help of relevant circuit diagram.