## **III SEMESTER B.TECH (ELECTRICAL & ELECTRONICS ENGINEERING)**

## **END SEMESTER EXAMINATIONS NOV/DEC 2016**

## SUBJECT: DIGITAL ELECTRONIC CIRCUITS [ELE 2102]

**REVISED CREDIT SYSTEM**

| Time                        | : 3 Hours                                         | Date: 28 November 2016                                                                                                                                         | MAX. MARKS: 50      |

|-----------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Instructions to Candidates: |                                                   |                                                                                                                                                                |                     |

|                             | Answer <b>ALL</b> questions.                      |                                                                                                                                                                |                     |

|                             | <ul> <li>Missing data may be suita</li> </ul>     | ble assumed.                                                                                                                                                   |                     |

| 1A.                         | Design a logic circuit to im                      | plement f (a,b,c,d) = $\sum m(1,3,5,9,11,12,13,14) +$                                                                                                          | d(2.6.8) using      |

|                             | minimum number of NOR gat                         |                                                                                                                                                                | (03)                |

| 1B.                         | Ū.                                                | •                                                                                                                                                              |                     |

| 10.                         |                                                   | a(0,5,8,9,10,21,26,29,30) + d(1,7,12,13,14,15,16,17)                                                                                                           |                     |

| 4.0                         | using VEM technique                               |                                                                                                                                                                | (05)                |

| <b>1C</b> .                 | Using 74LS194 wired as a rig                      | ht shift register implement Johnson counter.                                                                                                                   | (02)                |

| 2A.                         | Decign a 4 hit hinary to gray                     | v code converter using 3 to 8 decoders. Residua                                                                                                                | l gatas may ba      |

| 2A.                         | used.                                             | code converter dsing 5 to 6 decoders. Residua                                                                                                                  | (04)                |

| 2B.                         | Realize the Boolean expression                    | on                                                                                                                                                             |                     |

|                             | $f(w,x,y,z) = \sum m(0,2,4,5,7,2)$                | 9,10,14)                                                                                                                                                       |                     |

|                             | multiplexers with variable                        | e structure. The first level should consist of two<br>les w and z on their select lines S1 and S0 , res<br>ist of a single 2-t0-1 line multiplexer with the va | spectively, and     |

| 20                          |                                                   | l hit in 4 to 2 Driverite and day with the hale of                                                                                                             |                     |

| 2C.                         | table                                             | l bit in 4 to 2 Priority encoder, with the help of                                                                                                             | (02)                |

|                             | tuble                                             |                                                                                                                                                                | (02)                |

| 3A.                         | -                                                 | a synchronous 3 bit counter which works as a<br>rol signal G=0 and as a mod-8 gray code coun<br>unter using T flip flops.                                      | -                   |

| 3B.                         | Using 74LS283 implement on                        | e digit BCD adder.                                                                                                                                             | (03)                |

| 3C.                         | Design a Divide by 10 counter                     | r using IC 7493                                                                                                                                                | (02)                |

|                             |                                                   |                                                                                                                                                                |                     |

| 4A.                         | Simplify f(A,B,C,D,E) =<br>McCluskey (QM) method. | $\sum m(1,8,21,28) + d(4,5,12,17,24,25,26,27,30)$                                                                                                              | using Quine<br>(04) |

| 4B.                         | Mention the different blocks                      | with their significance in the Algorithmic State                                                                                                               | nachine Chart.      |

|                             | Draw the ASM chart for a 4 to                     | 1 multiplexer.                                                                                                                                                 | (04)                |

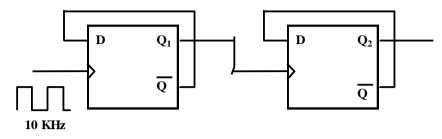

| <b>4C</b> .                 | Draw the output waveforms (                       | (Q1, Q2) of the circuit given in Figure Q4C.                                                                                                                   | (02)                |

|                             |                                                   |                                                                                                                                                                |                     |

- **5A.** AB flip flop has a characteristic equation  $Q^+ = BQ + A\overline{Q}$ . Construct AB flip flop using T Flip flop

- **5B.** In a 10 bit input stream, count the no of occurrence of the sequence 010 as a Mealy machine. Implement using D flip flop and IC 74LS90. *(06)*

Figure Q 4C

(04)