| Der Me   |  |  |  |  |  |

|----------|--|--|--|--|--|

| Reg. No. |  |  |  |  |  |

## MANIPAL INSTITUTE OF TECHNOLOGY Manipal University THIRD SEMESTER B.TECH (E & C) DEGREE END SEMESTER EXAMINATION NOV/DEC 2016 SUBJECT: ANALOG ELECTRONIC CIRCUITS (ECE - 2101)

| T | TA/E. 2 | <b>HOURS</b> |  |

|---|---------|--------------|--|

MAX. MARKS: 50

## **Instructions to candidates:**

- Answer **ALL** questions.

- Missing data may be suitably assumed.

- 1A. Design a single stage amplifier which gives a voltage gain of 5 without any change in the phase of the signal and an input impedance of 100 $\Omega$ . Assume  $\beta$ =100, V<sub>CC</sub>=2.5V, Is=10<sup>-16</sup>A, V<sub>A</sub>= $\infty$  and operating frequency of 700MHz.

- 1B. In the circuit of Fig. Q1 (B),  $\beta$ =100 and V<sub>A</sub>= $\infty$ . Calculate the value of I<sub>S</sub> such that the base-collector junction is forward biased by 200mV.

- 1C. A voltage dependent current source is constructed with K=20mA/V. What value of load resistance in Fig. Q1 (C) is necessary to achieve a voltage gain of 15?

$$R_{c} \neq 9 \text{ k}\Omega \qquad + \qquad - \downarrow V_{cc} = 2.5 \text{ V}$$

$$R_{p} \neq 1 \text{ k}\Omega \qquad V_{in} \qquad + \qquad + \qquad V_{1} \qquad V_{1} \neq R_{L} \qquad V_{out}$$

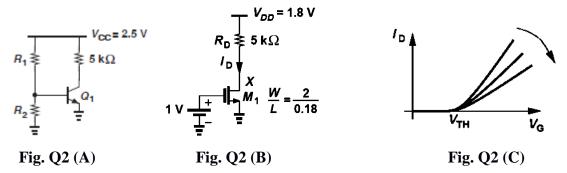

- 2A. The circuit of Fig. Q2 (A) must be designed for an input impedance of greater than  $10k\Omega$  and a  $g_m$  of at least  $1/(260\Omega)$ . If  $\beta=100$ ,  $I_S=2\times10^{-17}$ A, and  $V_A=\infty$ , determine the minimum allowable values of  $R_1$  and  $R_2$ . If the design is to be repeated for a  $g_m$  of at least  $1/(26\Omega)$ , show that no solution exists.

- 2B. In Fig. Q2 (B), calculate the bias current of M<sub>1</sub>. Assume  $\mu_n C_{ox} = 100\mu A/V^2$  and  $V_{TH} = 0.4V$ . Verify if the device is operating in saturation. If the gate voltage increases by 10mV, what is the change in the drain voltage? Determine the value of W/L that places M<sub>1</sub> at the edge of saturation. Calculate the drain voltage change for a 1mV change at the gate.

- 2C. In the I<sub>D</sub>–V<sub>G</sub> plot of Fig. Q2 (C), the arrow indicates (i) Decreasing channel length 'L' (ii) Decreasing oxide thicknesses 't<sub>ox</sub>' (iii) Increasing channel width 'W'. Identify the correct statements. Correct the statements which are incorrect.

(5+3+2)

(5+3+2)

ECE -2101

Page 1 of 3

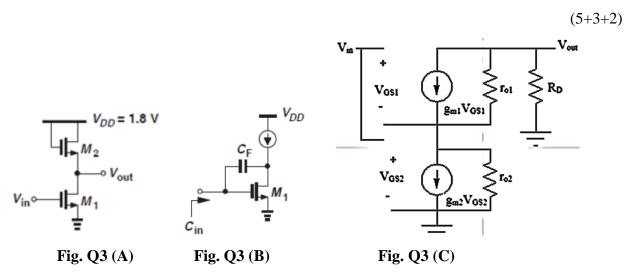

- 3A. For the amplifier circuit shown in Fig. Q3 (A), neglecting channel length modulation, derive the expression for the voltage gain. Assuming a power budget of 1mW and an overdrive voltage of 200mV for M<sub>1</sub>, design the circuit for a voltage gain of 4.

- 3B. Using Miller's theorem, determine the input capacitance of the circuit shown in Fig. Q3 (B). Assume  $\lambda > 0$ .

- 3C. Construct the MOSFET circuit using the small signal model shown in Fig. Q3 (C). Is your solution unique?

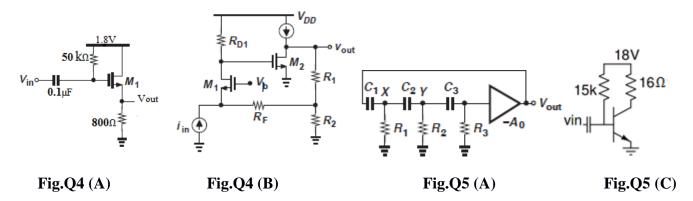

- 4A. Analyze the circuit shown in Fig. Q4 (A) at low and high frequencies and plot its frequency response. The circuit is connected to a load capacitance of 10pF. Assume C<sub>GS</sub>=250fF, C<sub>GD</sub>=80fF, C<sub>DB</sub>=100fF,  $\lambda$ =0, V<sub>GS</sub>=0.8V, V<sub>TH</sub>=0.5V and  $\mu_n C_{ox} = 100\mu A/V^2$ .

- 4B. Determine the closed loop gain, I/O impedances of the circuit shown in Fig. Q4 (B).

- 4C. Prove that negative feedback improves the bandwidth of the system.

(5+3+2)

- 5A. Determine the oscillating frequency of RC phase shift oscillator shown in Fig. Q5 (A).

- 5B. Determine the power efficiency of class B push pull amplifier and list its merits and demerits.

- 5C. For the circuit shown in Fig. Q5 (C), if the input signal has a peak current of 1 mA, determine the power efficiency. Assume  $\beta$ =50.

(5+3+2)