| _        |  |  |  |  |  |

|----------|--|--|--|--|--|

| Reg. No. |  |  |  |  |  |

|          |  |  |  |  |  |

MANIPAL INSTITUTE OF TECHNOLOGY Manipal University

## FIRST SEMESTER M.TECH (DEAC & ME) DEGREE END SEMESTER EXAMINATION NOV/DEC 2015 SUBJECT: ANALOG AND RF VLSI DESIGN [ECE - 503]

## **TIME: 3 HOURS**

MAX. MARKS: 50

Instructions to candidatesAnswer ANY FIVE full questions.

• Missing data may be suitably assumed.

- 1A. Give the circuit of double cascode current sink. Using small signal ac model, derive the expression for output resistance. What is the minimum output voltage across the current sink?

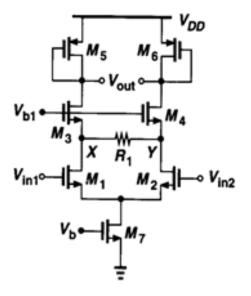

- 1B. Apply half-circuit concept to find small-signal differential voltage gain for the circuit given in FIG. 1B. Given that all transistors in the circuit are saturated. Assume  $\lambda \neq 0$ ,  $\gamma \neq 0$ .

- <sup>1C.</sup> Show that a negative capacitance can be realized using an amplifier block having suitable gain A and a passive capacitance C. State the principle used.

(5+3+2)

- 2A. Discuss the improved wide-swing cascode current mirror circuits.

- 2B. In a NMOS source follower circuit with a current sink load, all transistors have W/ L = 100  $\mu$ m/ 2  $\mu$ m. Given that I<sub>bias</sub> =100  $\mu$ A,  $\eta = 0.1$ , K<sub>n</sub> = 75  $\mu$ A/V<sup>2</sup>, K<sub>p</sub> = 30  $\mu$ A/V<sup>2</sup>, r<sub>ds-n</sub> = 128 kΩ, r<sub>ds-p</sub> = 192 kΩ. Find small-signal voltage gain and output resistance.

- 2C. Define the term single parameter sensitivity. Derive an expression for sensitivity of output current  $I_o$  with respect to  $V_{DD}$  in a cascode current sink circuit. Give your comments.

(5+3+2)

- 3A. Give the schematic circuit of a PMOS based folded cascode amplifier. Derive the exact expression for small-signal voltage gain and output resistance. Also give the approximate expression for voltage gain.

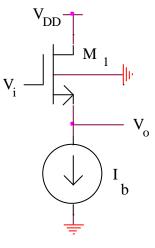

- 3B. Show that the small-signal voltage gain neglecting channel length modulation effect for the circuit shown in FIG. 3B is given by  $A_v = 1/(1 + \eta)$ .

- <sup>3C.</sup> Give the circuit diagram of folded cascade opamp topology and salient features.

(5+3+2)

- 4A. Show how a variable gain amplifier (VGA) is implemented using differential amplifier. Discuss the two Gilbert cell topologies.

- 4B. Consider the circuit of nMOS CG amplifier with a pMOS current source load. M<sub>1</sub> is the input MOS device and M<sub>2</sub> is the output MOS of M<sub>2</sub>-M<sub>3</sub> current source circuit. Assume that the CG amplifier has a bias current of 0.1mA and that all transistors have a W/L of 100  $\mu$ m/2  $\mu$ m. Given that K<sub>n</sub> = 50  $\mu$ A/V<sup>2</sup>, K<sub>p</sub> = 17  $\mu$ A/V<sup>2</sup>, g<sub>ds,n</sub> = 10  $\mu$ mho, g<sub>ds,p</sub> = 5  $\mu$ mho,  $\eta$  = 0.1.Compute small-signal voltage gain.

- 4C. Derive the expression for small-signal common-mode voltage gain in a source-coupled NMOS differential amplifier neglecting second-order effects.

(5+3+2)

- 5A. Give the CMOS circuit of balanced Operational Transconductance Amplifier? Compare OTA and op-amp with respect to following: [i] area [ii] input and output resistance [iii] gain [iv] bandwidth

- <sup>5B.</sup> Explain the channel length modulation. Derive the expression for channel length modulation parameter  $(\lambda)$ .

- <sup>5C.</sup> Discuss the structure of double poly capacitor.

(5+3+2)

- 6A. Explain the basic PLL block diagram with necessary analog building blocks. Show how PLL can be used for FM demodulation.

- 6B. With appropriate figures, explain how the differential operation can reduce following: [i] effect of supply noise [ii] Effect of coupled noise from digital clock signal.

- 6C. State the principle used in the design of RF Mixers.

(5+3+2)

FIG. 1B

FIG. 3B