# Manipal Institute of Technology, Manipal

(A Constituent Institute of Manipal University)

3

3

4

# FIFTH SEMESTER B.TECH (INSTRUMENTATION & CONTROL ENGINEERING)

## END SEMESTER EXAMINATIONS, NOV/DEC 2015

SUBJECT: DIGITAL SYSTEM DESIGN [ICE 311]

Time: 3 Hours

MAX. MARKS: 50

#### Instructions to Candidates:

- ✤ Answer ANY FIVE FULL questions.

- ✤ Missing data may be suitably assumed.

- **1A.** Determine the prime-implicants of the function:

$$F(w, x, y, z) = \sum_{i=1}^{n} (1,4,6,7,8,9,10,11,15)$$

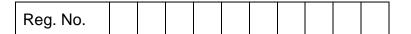

**1B.** Find the static-0 hazards in the following  $\overline{\text{circuit}}$ .

Redesign the circuit so that it is free of static hazards. Use gates with at most three inputs.

**1C.** For the input and output sequence given below:

### Input=1010110101010 Output=0001000010101

Draw Mealy state graph and state table.

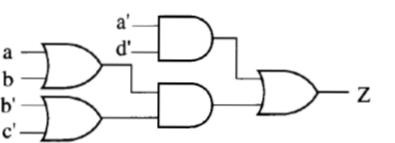

2A. Consider the following digital device in Fig. 2A. The timing characteristics of its components 3 are available in the table below. What are the timing characteristics of the overall device? Calculate the setup time and the minimum clock period for proper operation of the circuit.

| Device           | Propagation Delay<br>(Minimum) | Propagation Delay<br>(Maximum) | Setup Time | Hold Time |

|------------------|--------------------------------|--------------------------------|------------|-----------|

| D Flip Flop      | 4 ns                           | 8 ns                           | 10 ns      | 3 ns      |

| NAND Gate        | 3 ns                           | 6 ns                           | Х          | Х         |

| Bubbled AND Gate | 2 ns                           | 4 ns                           | Х          | Х         |

- **2B.** Draw a complete Y-chart showing different levels and domains of abstraction.

- (a) Write VHDL code for a full adder using logic equations.

- (b) Write structural VHDL code for a 4-bit full adder using module defined in (a) as a component.

- **3A.** Consider the following VHDL code:

2C.

entity O3 is port(A,B,C,F,Clk:in bit; E:**out** bit); end O3: architecture Qint of Q3 is signal D,G:bit; begin process(clk) begin if clk'event and clk='1' then D<=A and B and C: G<=not A and not B: E<=D or G or F: end if: end process; end Oint:

- (a) Draw a block diagram for the circuit. (at block level)

- (b) Give the circuit generated by the preceding code. (at gate level)

- **3B.** For the state table shown below, write full behavioral code:

| Present state | Next state |            | Output |

|---------------|------------|------------|--------|

|               | X=0        | X=1        |        |

| SO            | <b>S</b> 1 | <b>S</b> 0 | 00     |

| S1            | <b>S</b> 0 | S2         | 01     |

| S2            | S2         | <b>S</b> 1 | 10     |

- **3C.** Explain working of a  $4 \times 4$  keypad scanner using a flowchart.

- 4A. Explain case statements using example of column scanning logic.

- 4B. For a 10 MHz clock and active low reset, generate a single o\_done signal at the end of 100 4 μs. Counter is operational only when i\_counter\_start is high. Write a VHDL code (signal declarations & process only) and the timing diagram for the above.

- **4C.** Briefly explain the different operators used in VHDL.

- **5A.** Write a test bench to verify the working of a JK flip-flop.

Page 2 of 3

3 4

3

4

3

4

2

4

**5B.** Implement the following state table using ROM and flip-flops and illustrate the design using **3** a truth table and block diagram.

| Present state | Next state |            | Output |     |

|---------------|------------|------------|--------|-----|

|               | X=0        | X=1        | X=0    | X=1 |

| SO            | S1         | S0         | 0      | 0   |

| S1            | S2         | S0         | 0      | 0   |

| S2            | S4         | S3         | 0      | 0   |

| S3            | S1         | <b>S</b> 0 | 1      | 0   |

| S4            | S4         | S0         | 0      | 0   |

**5C.** Find a minimum-row PLA to implement the following three functions:

$$f(A, B, C, D) = \Sigma m(3, 6, 7, 11, 15)$$

$$q(A, B, C, D) = \Sigma m(1, 3, 4, 7, 9, 13)$$

$g(A, B, C, D) = \Sigma m(1,3,4,7,9,1)$ With diagrams explain the different types of FPGA architectures. 6A.

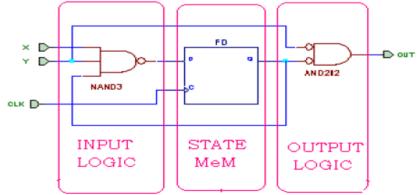

**6B.** Find the minimum set of tests that will test all stuck-at-1 faults in the following circuit. For 3each test, specify the faults tested.

6C. Explain boundary scan testing with a neat diagram.

3

3

4