| Reg. No. |  |  |  |  |  |  |  |  |  |  |

|----------|--|--|--|--|--|--|--|--|--|--|

|----------|--|--|--|--|--|--|--|--|--|--|

3

4

## FIFTH SEMESTER B.TECH (INSTRUMENTATION & CONTROL ENGG.) END SEMESTER EXAMINATIONS, NOV/DEC 2016

SUBJECT: DIGITAL SYSTEM DESIGN [ICE 311]

Time: 3 Hours MAX. MARKS: 50

## Instructions to Candidates:

- **❖** Answer **ANY FIVE FULL** questions.

- Missing data may be suitably assumed.

- **1A.** Write the truth table for following equation:

$F = (A \oplus B)C + A'(B \oplus C)$

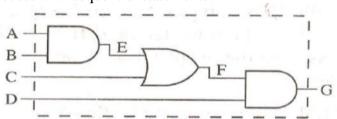

- **1B.** Write VHDL code for the following circuit. Assume that the gate delays are negligible.

- (a) Use concurrent statements.

- (b) Use a process with sequential statements.

- **1C.** What do you mean by hazards in combinational networks? Explain the types of hazards.

- **2A.** Explain the different Scalar data types used in VHDL. Illustrate each with examples. **4**

- **2B.** Draw a complete Y-chart showing different levels and domains of abstraction.

- **2C.** Explain the structure of a VHDL program.

- **3A.** Write a sequential VHDL code for a T flip-flop.

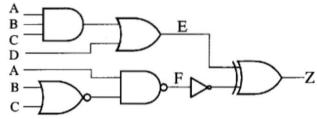

- **3B.** Write a VHDL description of the following combinational circuit using concurrent statements.

- **3C.** Explain procedures and write a procedure for sorting a greater value when two values are provided.

- **4A.** Write a structural VHDL code for a full adder assuming that full adder has been defined as a component.

ICE 311 Page 1 of 2

| <b>4B.</b> | Briefly explain the different operators used in VHDL.                           |   |  |  |

|------------|---------------------------------------------------------------------------------|---|--|--|

| 4C.        | Write a test bench to verify the working of a JK flip-flop.                     |   |  |  |

| 5A.        | Briefly explain how ROMs are classified.                                        |   |  |  |

| 5B.        | Explain the different types of FPGA programming technologies.                   |   |  |  |

| 5C.        | Find a minimum-row PLA to implement the following two functions:                | 3 |  |  |

|            | $f(A,B,C,D) = \Sigma m(3,4,6,9,11)$<br>$g(A,B,C,D) = \Sigma m(2,4,8,10,12,14)$  |   |  |  |

| <i>-</i> 1 | $h(A, B, C, D) = \Sigma m(3,6,7,10,11)$                                         | _ |  |  |

| 6A.        | With a block diagram explain the operation of a programmable I/O block in FPGA. | 6 |  |  |

| 6B.        | Explain scan testing with a block diagram.                                      | 4 |  |  |

\*\*\*\*\*\*\*\* END \*\*\*\*\*\*\*\*

ICE 311 Page 2 of 2