## MANIPAL UNIVERSITY

## SCHOOL OF INFORMATION SCIENCES FIRST SEMESTER MASTER OF ENGINEERING - ME (VLSI DESIGN) DEGREE EXAMINATION - NOVEMBER 2017

DATE: Tuesday, November 21, 2017 TIME: 10:00AM - 1:00PM Verification [EDA 617]

Marks: 100 Duration: 180 mins.

## Δ

## Answer all the questions.

- Explain the following commonly used terminology in verification: (10)

- (a) SoC

- (b) BFM

- (c) Regression

- (d) Constrained Random Verification

- Explain with examples about the following SystemVerilog (10) data types:

- (a) Enumerated

- (b) Dynamic arrays

- (c) Unions

- (d) Queues

- (e) Logic

- Explain the difference between shallow copy and deep copy operations. Give examples with descriptive diagrams to substantiate your answer.

- Write the output of the following code segment (10)

module test();

class A;

randint y;

constraintplk  $\{y > 2*2*2; y < 7;\}$

endclass

class B extends A;

```

endclass

class C extends B:

constraintrpr \{y > 3; y < 7;\}

endclass

Aa;

B b;

C c:

initial

begin

a=new();

b=new();

c=new();

if(a.randomize() == 1)

display("(1) y=\%0d",a.y);

else

$display("(1) Randomization Failure");

if(b.randomize() == 1)

display("(2) y=\%0d",b.y);

else

$display("(2) Randomization Failure");

if(c.randomize() == 1)

display("(3) y=\%0d",c.y);

else

$display("(3) Randomization Failure");

end

endmodule

Can the following scenarios occur? Give examples that

(10)

substantiate your answer.

1. (a) 100% code coverage of a design has been

achieved, but not 100% functional coverage.

2. (b) 100% functional coverage of a design has been

achieved, but not 100% code coverage.

A) Define a cover group 'mcg' with a cover point 'mrngkind' (10)

```

constraintplk  $\{y > 5; y < 7;\}$

5)

6)

```

a) 'zerobin' {0}

b) 'lobin' {{1:4}, 10}

c) 'hibin' {9: $}

d) 'miscbin' - the rest of values

where, 'mrngkind' is a bit-vector with range [0:15].

(5 marks)

B) What is the need for verification?

(5

marks)

7)

(10)

Write the output of the following code segment:

program test;

task print(intdisplayvar);

$display("%0d", displayvar);

endtask

initial

begin

for(inti=0; i < 5; i++)

begin

int j;

j = i;

fork

print(j);

join none

end

wait fork;

end

endprogram

(10)

8)

Write (code) a concurrent assertion in SystemVerilog to:

check whether a signal 'mysig' goes high at any random

point of time during the entire simulation.

The other signal names of interest while writing this

assertion are 'clk' and 'reset'.

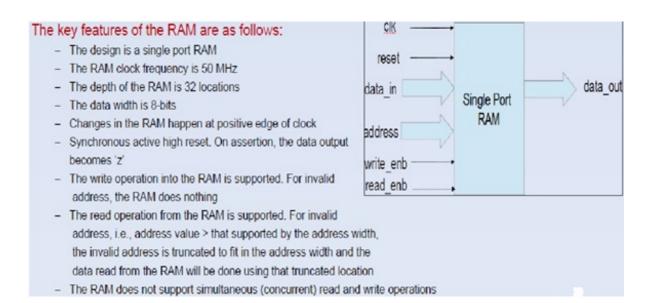

Write out the verification plan for a single-port RAM, the

9)

(10)

specifications of which are as follows:

```

using bin definitions as:

Include all scenarios that you can think of, including corner cases in your verification plan.

10)

Code ONLY the **monitor** module of the testbench for the single-port RAM, the specifications of which are already given in question number 10.

----End-----