## SEVENTH SEMESTER B.TECH. (INSTRUMENTATION AND CONTROL ENGG.) **END SEMESTER EXAMINATIONS, NOV - 2017**

SUBJECT: VLSI DESIGN [ICE 4004]

Time: 3 Hours MAX. MARKS: 50

## Instructions to Candidates:

- ❖ Answer **ALL** the questions.

- Use neat diagrams where ever needed.

- Illustrate the nMOS fabrication process with diagrams. **1A**

- 4

- 1**B** Obtain the expression for drain to source current in non-saturated region of a MOSFET.

- 3

- 1C Determine the pull-up to pull-down ratio for an nMOS inverter driven by another nMOS inverter.

- 3

- An inverter uses FETs with  $\beta_n=2.1 \text{ mA/V}^2$  and  $\beta_n=1.8 \text{ mA/V}^2$ . The threshold voltages **2A** are given as  $V_{tn}=0.6 \text{ V}$  and  $V_{tp}=-0.7 \text{ V}$  and the power supply has a value of  $V_{DD}=5 \text{ V}$ . The parasitic FET capacitance at the output node is estimated to be C<sub>FET</sub>=74 fF.

- 1. Find the midpoint voltage V<sub>M</sub>.

- 2. Find the values of  $R_n$  and  $R_p$ .

- 3. Calculate the rise and fall times at the output when C<sub>L</sub>=0.

- 4. Calculate the rise and fall times when an external load of value C<sub>L</sub>=115 fF is connected to the output.

- **2B** Sketch a transistor-level schematic and stick diagram/layout for the following function:

$$Y = \overline{AB + C.(A + B)}$$

- **2C** What is body effect? How does it affect the operation of a MOSFET?

- 2

Draw the equivalent RC circuit of a 2-input XOR gate. **3A**

3

4

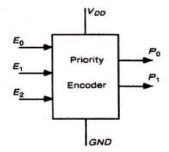

**3B** Construct a color-coded stick diagram to implement a priority encoder as in the following table:

| E <sub>2</sub> | E <sub>1</sub> | E <sub>0</sub> | P <sub>1</sub> | $P_0$ |

|----------------|----------------|----------------|----------------|-------|

| 0              | 0              | 0              | 0              | 0     |

| 0              | 0              | 1              | 1              | 1     |

| 0              | 1              | 0              | 1              | 0     |

| 0              | 1              | 1              | 1              | 0     |

| 1              | 0              | 0              | 0              | 1     |

| 1              | 0              | 1              | 0              | 1     |

| 1              | 1              | 0              | 0              | 1     |

| 1              | 1              | 1              | 0              | 1     |

4

ICE 4004 Page 1 of 2 3C Sketch a transistor-level schematic of a JK flip-flop.

4A Illustrate the design flow of a mixed-signal system with a flowchart.

4B Briefly explain the types of basic logic cells employed in a programmable ASIC.

4C Implement the following state table using a ROM and two D flip-flops:

| Present    | Next State     |                | Output (Z) |       |  |

|------------|----------------|----------------|------------|-------|--|

| State      | X = 0          | X = 1          | X = 0      | X = 1 |  |

| So         | S <sub>0</sub> | S <sub>1</sub> | 0          | 1     |  |

| S,         | S <sub>2</sub> | S <sub>3</sub> | 1          | 0     |  |

| <b>S</b> , | S,             | S <sub>3</sub> | 1          | 0     |  |

| S,         | S,             | S <sub>2</sub> | 0          | 1     |  |

5A Implement a 4:1 MUX using a 4-input LUT based FPGA configurable logic block.

5B Briefly explain the different fault types and models.

5C What are the essential circuit models required for Built-in-self-test (BIST)? Illustrate them with figures.

\*\*\*\*\*\*\*\*\*

ICE 4004 Page 2 of 2