Reg. No.

## MANIPAL INSTITUTE OF TECHNOLOGY MANIPAL

(A constituent unit of MAHE, Manipal)

## **III SEMESTER B.TECH (ELECTRICAL & ELECTRONICS ENGINEERING)**

## **MAKE UP EXAMINATIONS, MAY 2018**

## SUBJECT: ANALOG ELECTRONIC CIRCUITS [ELE 2105]

**REVISED CREDIT SYSTEM**

| Time:                       | 3 Hours Date: 16 MAY 2018                                                                                                                                                                                                                                                                                                                                                                                                                             | Max. Marks: 50                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Instructions to Candidates: |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |

|                             | <ul> <li>Answer ALL the questions.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |                                |

|                             | <ul> <li>Missing data may be suitably assumed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                             |                                |

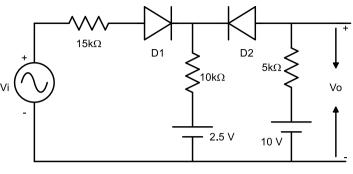

| 1A.                         | In the figure as shown in fig.Q1A, if Vi has a peak of 20 V, then draw the output and transfer characteristics.                                                                                                                                                                                                                                                                                                                                       | waveform <b>4</b>              |

| 1B.                         | Discuss the importance of Diode based Clampers with suitable examples.                                                                                                                                                                                                                                                                                                                                                                                | 3                              |

| 1C.                         | Write a note on Zener Voltage regulator.                                                                                                                                                                                                                                                                                                                                                                                                              | 3                              |

| 2A.                         | Define transconductance of MOSFET. Hence derive the equations gove relationship between transconductance, current, aspect ratio and gate overdri of the MOSFET.                                                                                                                                                                                                                                                                                       | 0                              |

| 2B.                         | Discuss the different regions of operation of MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                 | 3                              |

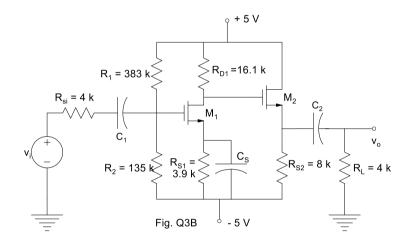

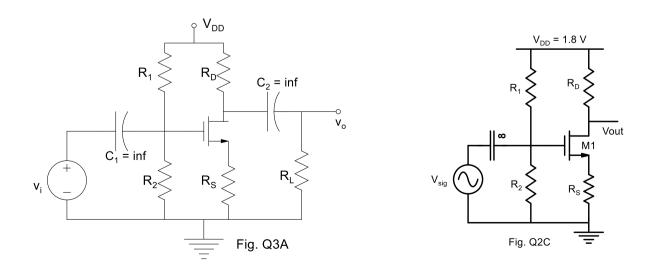

| 2C.                         | Design the circuit shown in Fig. Q2C for a voltage gain of 5V/V and a power budg<br>Assume that the voltage divider branch consumes 5% of total power and vol<br>across Rs is equal to the overdrive voltage of the transistor. Also assume<br>$V_{TH} = 0.4$ V, $\mu$ nCox = 200 $\mu$ A/V2, $\lambda$ =0.                                                                                                                                           | ltage drop                     |

| 3A.                         | For the NMOS common source amplifier shown in Fig. Q3A, the transistor param $V_{th} = 0.8 \text{ V}$ , $\mu_n C_{ox} (W/2L) = 1 \text{ mA}/V^2$ , $V_{DD} = 5 \text{ V}$ , $R_s = 1 \text{ k}\Omega$ , $R_D = 4 \text{ k}\Omega$ , $R_1 = 225 \text{ k}\Omega$ , $\Omega_1$ calculate the quiescent values $I_{DQ}$ and $V_{DSQ}$ . Draw the small signal model determine the small signal gain for $R_L$ is infinite. Neglect Channel length modula | $P_{1}, R_{2} = 175$ and hence |

| 3B.                         | Determine the small signal voltage gain of the multistage cascade circuit shown i<br>Draw the small signal model and neglect channel length modulation.                                                                                                                                                                                                                                                                                               | n Fig. Q3B. <b>5</b>           |

| 4A.                         | Bandwidth of an amplifier lies between 100 Hz and 100 kHz. Find frequency which voltage gain is less than 1 dB from mid-band value.                                                                                                                                                                                                                                                                                                                   | range over 3                   |

| 4B.                         | Design an NMOS current mirror with $V_{DD}$ =5V, $V_{SS}$ =0V, $I_{ref}$ =100µA. For the transistors L=10µm, W=100µm, $V_{TH}$ =1V, $\mu_n C_{ox}$ = 20µA/V <sup>2</sup> .                                                                                                                                                                                                                                                                            | e matched <b>3</b>             |

| 4C.                         | State and prove Millers theorem.                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                              |

| 5A.                         | Classify the power amplifiers based on the operating point.                                                                                                                                                                                                                                                                                                                                                                                           | 2                              |

| 5B.                         | Derive the expression for conversion efficiency of Class A Power amplifier.                                                                                                                                                                                                                                                                                                                                                                           | 4                              |

| 5C.                         | Derive expressions for Differential gain, Common mode gain and CMRR Differential Pair.                                                                                                                                                                                                                                                                                                                                                                | of a MOS <b>4</b>              |