Reg. No.

MANIPAL INSTITUTE OF TECHNOLOGY

(A constituent Institution of MAHE, Manipal)

## III SEMESTER B. TECH (ELECTRICAL & ELECTRONICS ENGINEERING) MAKE UP EXAMINATIONS, JANUARY 2019

## SUBJECT: ANALOG ELECTRONIC CIRCUITS [ELE 2105]

REVISED CREDIT SYSTEM

| Time                        | e: 3 Hours D                                                                                 | ate: 02, January 2019                                                                                                  | Max. Marks: 50                                     |

|-----------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Instructions to Candidates: |                                                                                              |                                                                                                                        |                                                    |

|                             | ✤ Answer ALL the questions.                                                                  |                                                                                                                        |                                                    |

|                             | <ul> <li>Missing data may be suitably a</li> </ul>                                           | issumed.                                                                                                               |                                                    |

|                             |                                                                                              |                                                                                                                        |                                                    |

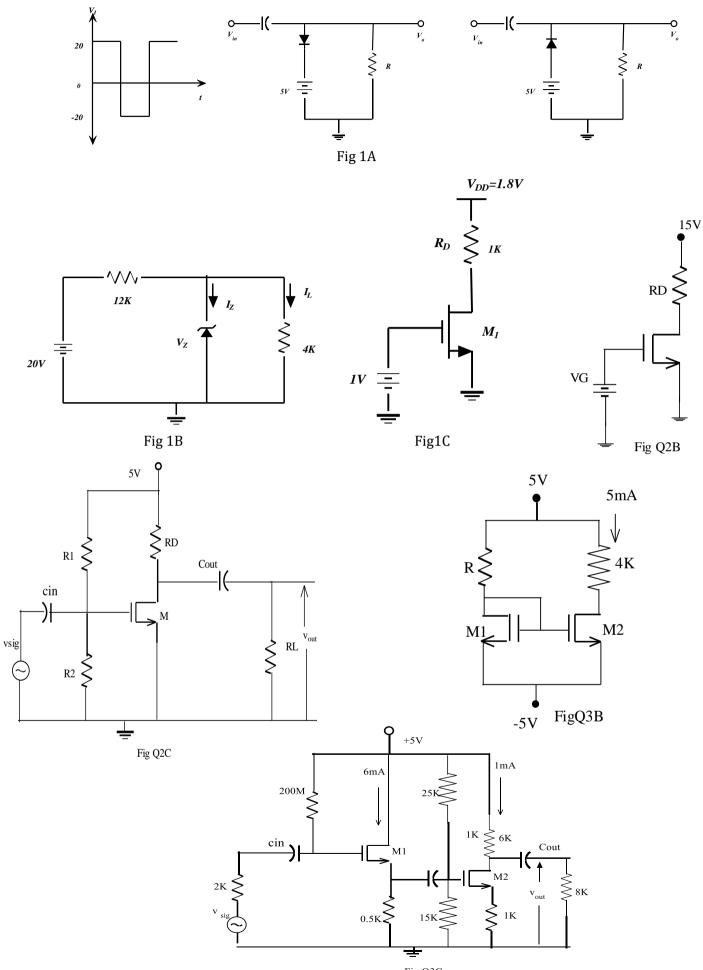

| 1A.                         | Sketch the steady state output volt<br>Assume ideal diodes.                                  | age $v_0$ for each circuit in Figure 1A with inpu                                                                      | t voltage v <sub>I</sub> .<br><b>(05)</b>          |

| 1B.                         | Consider the circuit shown in Figur<br>and the power dissipated in the did                   | e 1B. The Zener diode voltage is $V_Z = 3.9V$ . Det ode.                                                               | ermine I <sub>Z</sub> , I <sub>L</sub> <b>(03)</b> |

| <b>1C</b> .                 | Assume = 0 , compute $\frac{W}{L}$ of $M_1$ in saturation. Given $\mu_n C_{ox} = 200 \mu A/$ | Figure 1C, such that the device operates at $V^2$ , $V_{TH} = 0.4V$                                                    | the edge of<br>(02)                                |

| 2A.                         | Derive the on resistance of the MO source voltage dependent.                                 | SFET in the triode region. Prove that resistan                                                                         | ce is gate to<br><b>(02)</b>                       |

| 2B.                         |                                                                                              | the Fig Q2B, find drain current, and volt<br>n if $V_{th} = 1.5V$ , $\mu_n C_{ox} \frac{W}{L} = 10mA/V^2$ , and        | age <i>V<sub>DS</sub></i> ,and                     |

|                             | $i) V_G = 1V, R_D = 2K$                                                                      | ii) $V_G = 3V, R_D = 1K.$                                                                                              | (05)                                               |

| 2C.                         |                                                                                              | for the voltage gain of 8dB with the Vth=0.6V.Current through R1, R2 is 100 Find $\frac{W}{L}$ , R1, R2. Refer Fig 2C. |                                                    |

| 3A.                         | Draw the circuit diagram of commo<br>derive small signal gain for the sam                    | on gate configuration, Develop the small signal<br>ie.                                                                 | model and<br><b>(06)</b>                           |

| 3B.                         | Determine the resistance R and                                                               | $V_{GS}$ required for a current mirror $({}^W/_L)_2$                                                                   | $\frac{2}{(W_{/L})_{1}} = 5,$                      |

|                             | $(\mu_n C_{ox} \frac{W}{L}) = 2mA/V^2$ , Vth=1V. Refe                                        |                                                                                                                        | (02)                                               |

| 3C.                         | Determine the overall small signal the small signal model for the same                       | gain for the cascaded MOS amplifier shown in I<br>e. Assume Vth=0.4V                                                   | Fig 3C. Draw<br><b>(02)</b>                        |

| 4A.                         | Draw the circuit of a RC coupled a importance of all the resistors and                       | amplifier and its typical frequency response.<br>capacitors.                                                           | Explain the<br>(07)                                |

| <b>4B.</b>                  | State and Prove Millers theorem.                                                             |                                                                                                                        | (03)                                               |

| 5A.                         | Classify the Power Amplifiers base                                                           | d on operating point                                                                                                   | (02)                                               |

| 5B.                         |                                                                                              | oupled class A power Amplifier and derive the                                                                          |                                                    |

| 5C.                         | for conversion efficiency, hence de<br>Write a note on Differential Amplif                   | termine the maximum value.                                                                                             | (04)<br>(04)                                       |

| FLF 2105 Page 1 of 2        |                                                                                              |                                                                                                                        |                                                    |