| Reg. No. |  |  |  |  |  |  |  |  |  |  |  |

|----------|--|--|--|--|--|--|--|--|--|--|--|

|----------|--|--|--|--|--|--|--|--|--|--|--|

## I SEMESTER M.TECH. (INDUSTRIAL AUTOMATION AND ROBOTICS) END SEMESTER EXAMINATIONS, NOV-DEC2018

SUBJECT: ANALOG AND DIGITAL ELECTRONICS [MTE 5131]

Time: 3 Hours

MAX. MARKS: 50

04

## Instructions to Candidates:

✤ Answer ALL the questions.

**1C.** Design an 8-bit serial in serial out shift register.

Data not provided may be suitably assumed

1A. Design a circuit using OP-AMP for diode match finder application. 03

- 1B. Design a circuit with an adjustable feedback gain to record 4 musical 03 instruments in parallel with a singer for a common amplified signal.

- 2A. Explain grey codes conversion from BCD and identify the use of gray codes in 04 shaft position encoders.

- **2B.** Design a circuit using timer to generate frequency of 2KHz with 50% duty **06** cycle.

- **3A.** Design a BCD to seven segment driver circuit using active low output decoders. **05**

- **3B.** Design a synchronous 3 bit up-down counter with state timing diagram. **05**

- **4A.** Compare the working principles of rectifier circuit with a clipper circuit for **05** analog input signals using OP-AMP.

- **4B.** Add the following unsigned binary numbers and perform 2's complement: **05** a. 1111110 and 101111

- b. 11010010 and 100011

- c. 10000001 and 100110

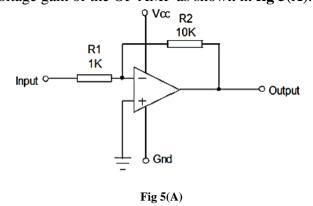

5A. Calculate the voltage gain of the OP AMP as shown in fig 5(A).

- **5B.** Construct a truth table for 8421-2421 BCD numbers conversion. **03**

- 5C Design a 4 bit parallel in serial out shift register and paraphrase data movement 05 in each clock pulse. (Taking the data flow 1111).