# **Question Paper**

Exam Date & Time: 24-Nov-2018 (10:00 AM - 01:00 PM)

### MANIPAL ACADEMY OF HIGHER EDUCATION

SCHOOL OF INFORMATION SCIENCES

FIRST SEMESTER MASTER OF ENGINEERING - ME (VLSI DESIGN)

#### High Level Digital Design [EDA 611]

Marks: 100

## Duration: 180 mins. END SEMESTER DEGREE EXAMINATION NOVEMBER 2018

#### Answer all the questions.

| Answei |                                                                                                         |      |

|--------|---------------------------------------------------------------------------------------------------------|------|

| 1)     | Implement the $F = \sum WXYZ(0, 2, 5, 7, 9, 11, 12, 15)$ logic                                          | (10) |

|        | function using multiplexer                                                                              |      |

| 2)     | Design and explain the following with neat diagram<br>a. D-Latch<br>b. D-FlipFlop<br>c. Scan D-FlipFlop | (10) |

| 3)     | Design a 1101 sequence detector using Moore Machine                                                     | (10) |

| 4)     | Design the following<br>a. All 0's Detector                                                             | (10) |

- b. All 1's Detector

- c. Equality Comparator

- <sup>5)</sup> Explain Carry Select Adder with neat diagram <sup>(10)</sup>

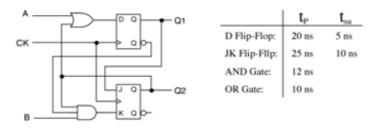

- <sup>6)</sup> For the given circuit, determine the delay of the longest <sup>(10)</sup> path.

- <sup>7)</sup> Design a Synchronous FIFO (10)

<sup>8)</sup> Explain the following (10)

- a. Single Ended I/O

|     | b. Differential Ended I/O                                                                              |      |

|-----|--------------------------------------------------------------------------------------------------------|------|

| 9)  | Brief explain the Split & retry operation                                                              | (10) |

| 10) | Design Real Time Clock with following features<br>a. Display - Hr : Min : Sec<br>b. Clock freq 500 KHz | (10) |

-----End-----