## **Question Paper**

Exam Date & Time: 07-May-2019 (09:30 AM - 12:30 PM)

## MANIPAL ACADEMY OF HIGHER EDUCATION

## INTERNATIONAL CENTER FOR APPLIED SCIENCES III SEMESTER B.Sc (Applied Sciences) IN **ENGINEERING END SEMESTER THEORY EXAMINATIONS APRIL/MAY 2019 ANALOG ELECTRONIC CIRCUITS [IEC 231 - S2]**

Marks: 100 Duration: 180 mins.

## Answer 5 out of 8 questions.

A)

(5) Draw and explain the input and output characteristics of Common Emitter Configuration. Indicate cut-off, saturation and active regions. Give the biasing A) conditions for all the three regions. B) (5) Write the expression for  $\alpha$  and  $\beta$  of a transistor. A BJT has  $\alpha = 0.99, I_B = 25 \mu A$ and  $I_{CR0} = 200 \text{ nA}$ . Find a) the DC collector current b) the dc emitter current and c) the percentage error in emitter current when leakage current is neglected. C) (5)Draw the fixed bias circuit. Design a fixed bias circuit using a silicon transistor having  $\beta$  value of 100 ,  $V_{CC}$ =10V and DC bias condition are  $V_{CE}$ =5V and  $I_{C}$ =5mA. D) (5) Plot the frequency response of RC coupled amplifier and explain how bandwidth is calculated using the response? 2) (5)

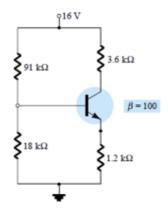

Q2A. For the voltage divider circuit using silicon transistor shown in figure Q2A, determine IB, IC, VCE, VC and VE. What are the advantages of self-bias circuit over fixed bias circuit?

FigQ2A

- In a multistage amplifier employing 5 stages, with voltage gains of 10, 15, 20, 25 and (5) 30dB. What is the overall voltage gain in dB. If 5mv is applied at the input of this amplifier, calculate the final output voltage

- An ideal voltage amplifier has infinite input impedance and zero output impedance. (5)

Justify this statement with the help of relevant diagram and expressions

- An amplifier has a voltage gain of 10, an input resistance of  $1K\Omega$  and an output resistance of  $10 \Omega$ . The amplifier is connected to a sensor that produces a voltage of 2V and has source resistance of  $100\Omega$  and to a load resistance of  $50\Omega$  what will be the output voltage of the amplifier Draw an equivalent circuit of the amplifier, sensor and load.

- 3) What is base width modulation in BJT? Explain with the help of suitable diagram (5)

A) B) (5)

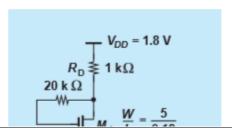

Calculate the maximum allowable gate voltage in Fig. Q3B, if M<sub>1</sub> must remain Saturated. Assume  $\mu_n C_{ox}=100~\mu\text{A/V}^2$  and  $V_{TH}=0.5V$

- Compare the common source amplifier with a common emitter amplifier and an emitter follower with a source follower.

- (5)

- Construct the high frequency model of a self-bias CS amplifier and obtain the expressions for cutoff frequencies.

- (10)

(5)

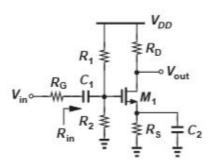

Design the CS stage of Fig. Q4A for a voltage gain of 5, an input impedance of 50KΩ, and a power budget of 5mW.Assume μ<sub>n</sub>C<sub>ox</sub> = 100 μA/V², Vth=0.5V, λ=0 and V<sub>DD</sub>=1.8V. Also assume a voltage drop of 400mV across Rs.

FigQ4A

B) (5)

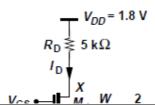

- i) Calculate the drain current of M1 in Fig Q4B if  $\mu_n C_{ox} = 100 \, \mu \text{A}/\text{V}^2$  V<sub>th</sub> =0.5V and  $\lambda$ = 0. What value of R<sub>D</sub> is necessary to reduce I<sub>D</sub> by a factor of two?

- ii) repeat the above problem if  $V_{DD}$  drops to 1.2V. Comment on your answer.

Fig Q4B

- With neat diagram explain working of n-channel enhancement type MOSFET. Plot ID- (5) VD Characteristics and mark the operating region.

- Draw the circuit diagram of a Hartley oscillator. Calculate the frequency of oscillations,

if L1=0.5 mH, L2=1 mH and C<sub>2</sub>=0.2 μF. What should be the value of C, if the frequency of oscillations were to be 12 KHz, with other components of the circuit remains same.

- B) State and explain Miller theorem. (5)

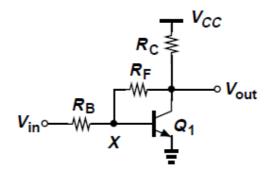

- C) For the circuit shown in Fig Q5C, draw the small signal model. Using Miller's theorem, determine Miller's input and output impedances for RF=50Kohms (5)

Fig Q5C

- D) What is crossover distortion? With the help of suitable diagrams, explain how it can be overcome? (5)

- A phase shift oscillator using transistor has RL=5.3 KΩ, R=4.6KΩ, C=0.01F.Calculate (5) the frequency of oscillation and also draw the circuit diagram of RC phase shift oscillator.

- B) State and explain the Barkhausen criteria for sustained oscillations (5)

- Derive the expression for voltage gain with feedback for a voltage series amplifier with  $^{(5)}$  gain A and feedback factor  $\beta$ .

- D)

A low pass filter circuit consisting of a resistor of 47KΩ in series with a capacitor of 47nF is connected across a 10V sinusoidal supply. Calculate the output voltage at a frequency of 100Hz and 10K Hz. Draw the circuit diagram of the filter.

- Draw the block schematic of i) Voltage shunt ii) Current series feedback amplifiers.

What is the effect of series and shunt feedback on the input and output resistance of an amplifier?

- B) Explain class A and class B power amplifiers with the help of output characteristic and (5)

load line. Illustrate their operation. What are the theoretical efficiencies of a series-fed class A and class B power amplifiers?

- C) (5) Draw the equivalent diagram of crystal and explain its working. Mention any two advantages of Crystal oscillators.

- (5)

- D) The parameters of the equivalent circuit of a crystal are given below: L = 0.4 H, Cs = 0.06 pF,  $R = 5k\Omega$ ,  $C_m = 1.0 \text{pF}$ . Determine the series and parallel resonant frequencies of the crystal.

(20)

8) Explain the following:

- i) Sense and return techniques

- Negative and positive feedback in amplifiers ii)

- iii) Second order effects in MOSFET

- Piezoelectric effect iv)

-----End-----