MANIPAL INSTITUTE OF TECHNOLOGY

(A constituent unit of MAHE, Manipal 576104)

## III SEM B.Tech (BME) DEGREE MAKE UP EXAMINATIONS, DEC/JAN 2019-20.

SUBJECT: ANALOG ELECTRONICS (BME 2151) (REVISED CREDIT SYSTEM) Friday, 20<sup>th</sup> December, 2019: 8.30 AM to 11.30 AM

**TIME: 3 HOURS**

MAX. MARKS: 50

**Instructions to Candidates:**

1. Answer ALL questions.

2. Draw labeled diagram wherever necessary

- 3. Assume suitable data, if missing

- 1. (A) An NPN Silicon transistor having  $\beta = 100$  is in common-emitter configuration, and 5 is biased by fixed bias method. The circuit parameters are

- $R_B = 530K\Omega, R_C = 3K\Omega$ , and  $V_{CC} = 6V$ . Draw the circuit diagram and determine (i) the d.c load line

- (ii) the operating point, and

- (iii) the stability factor

- (B) For the circuit drawn for question no.1(A), draw the a.c equivalent circuit and 3 determine the input and output impedances. Assume that the transistor is operated at room temperature, and output resistance of the transistor is infinity.

- (C) Draw the circuit diagram of a voltage-series feedback amplifier employing a BJT, and 2 derive expression for de-sensitivity (D).

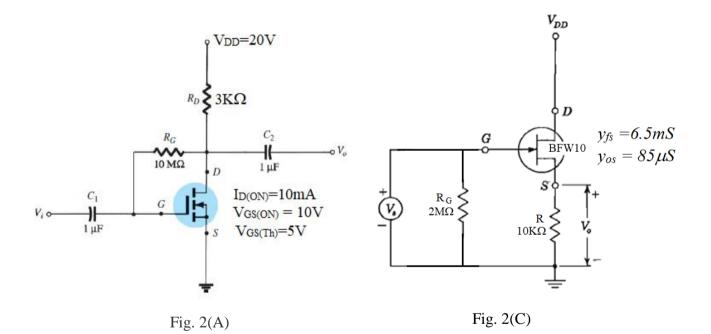

- 2. (A) Making use of transfer curve and bias line determine the operating point of the 5 Enhancement MOSFET circuit shown in figure 2(A).

- (B) In an UJT relaxation oscillator, the UJT and the circuit parameters are  $R_{BB} = 8K\Omega$ , 3  $\eta = 0.7$ ,  $R_1 = 0.2K\Omega$ ,  $R_E = 40K\Omega$ ,  $C_E = 0.12\mu$ F,  $V_V = 2V$ ,  $I_V = 10$ mA,

- $I_p = 10 \mu A$ ,  $V_D = 0.7 V$ , and  $V_{BB} = +12 V$ .

- (i) Determine value of  $RB_1$  and  $RB_2$  required, when  $I_E = 0mA$

- (ii) Calculate the value of  $V_{\text{E}}$  required to turn on the UJT

- (iii) Find the approximate frequency of oscillation

- (C) Determine the voltage gain and input impedance of the voltage-series feedback 2 amplifier shown in figure 2(C).

- 3. (A) An n-channel JFET in common-source configuration is biased using voltage-divider 5 biasing network with the source terminal resistor bypassed by a capacitor.

- (a) Draw the circuit diagram

- (b) Draw the small signal model, and

- (c) Prove that  $Z_i = R1 || R2$  and  $A_V = -g_m (r_d || R_D)$

- (B) For a JFET in fixed bias network, prove that the input impedance is  $R_{G}(\Omega)$ . 3

- (C) How does the conduction channel get pinched-off in a JFET?

2

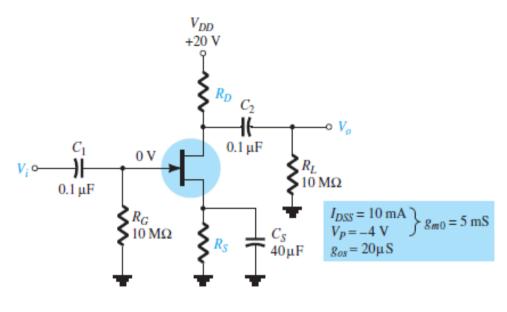

- 4. (A) For the FET circuit shown in figure no. 4(A), chose appropriate values of R<sub>D</sub> and R<sub>S</sub> 5 so as to establish a gain of 8 at  $V_{GSQ} = \frac{1}{4}V_P$ .

- (B) If a JFET in a fixed bias network has  $V_{GG} = -1V$ ,  $R_G = 2M\Omega$ ,  $V_{DD} = +12V$ , and  $R_D = 2K\Omega$ . And from the data sheet  $I_{DSS} = 8$ mA and  $V_P = -5V$ . Determine  $V_{GSQ}$  and  $I_{DQ}$ .

- (C) Draw typical drain and transfer characteristics of a depletion type MOSFET.

- 5. (A) For a Class-C power amplifier prove that the Power output is  $\frac{v_{cc}^2}{2r_c}$  and the efficiency 5 is 95%.

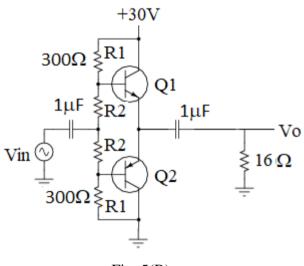

- (B) Compute the value of R2 required to provide trickle current for distortion free output 3 in the push-pull amplifier shown in figure no. 5(B). Assume  $V_{BE} = 0.7V$  for each transistor.

- (C) Design a current-series feedback amplifier to have an overall trans-conductance gain 2 of -1mA/V, a voltage gain of -4, and a de-sensitivity of 50. Make use of a NPN type BJT having  $h_{fe} = 150$ , and assume a signal source with a resistance of 1K $\Omega$ . Draw the labelled circuit diagram of the designed amplifier.

2

Fig. 4(A)

Fig. 5(B)