| Reg. No. |  |  |  |  |  |  |  |  |  |  |

|----------|--|--|--|--|--|--|--|--|--|--|

|----------|--|--|--|--|--|--|--|--|--|--|

## **V SEMESTER B.TECH. (COMPUTER SCIENCE AND ENGINEERING) END SEMESTER EXAMINATIONS, NOV/DEC 2019**

SUBJECT: COMPUTER ARCHITECTURE [CSE 3101]

## **REVISED CREDIT SYSTEM** (14/11/2019)

Time: 3 Hours MAX. MARKS: 50

## Instructions to Candidates:

- ❖ Answer **ALL** the questions.

- Missing data may be suitable assumed.

- **1A.** List and explain Flynn's classification of computer system.

What are the different data hazards introduced due to out-of-order execution of the following code **3M** sequence? Identify and demonstrate possible hazards that can be resolved.

> A: L.D F0, 0(R1) //L.D: Load the first element in array 0(R1) to F0

B: MUL.D F4, F0, F2 //MUL.D: Multiply

F4, 0(R1)

C: S.D F4, 0(R1) //S.D: store F4 in 0(R1)

E: L.D F0, 0(R1)F: F4, F0, F2 MUL.D

S.D

G:

**1C.** Consider a five-stage pipelined processor specified by the following reservation table in figure 1C. **4M**

|            | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|------------|---|---|---|---|---|---|---|---|

| <b>S1</b>  | X |   |   |   |   |   | Х |   |

| <b>S2</b>  |   | Х | Х |   |   |   |   |   |

| <b>S</b> 3 |   |   |   | Х |   |   |   |   |

| <b>S4</b>  |   | Х |   |   | Х |   |   | Х |

| <b>S</b> 5 |   |   |   |   |   | Х |   |   |

Figure 1C. Reservation table

- i) List the set of forbidden latencies and the collision vector.

- ii) Draw a state transition diagram showing all possible cycles without causing the collision in the pipeline.

- iii) List all the simple cycles from the state diagram. Identify the greedy cycles among the simple cycles. What is the MAL of this pipeline?

- Define maximum parallelism degree of a computer system. How to find the maximum parallelism 2A. degree of a computer system?

CSE 3101 Page 1 of 2 **3M**

- **2B.** For N number of PEs, prove that an Illiac routing functions are a subset of Barrel shifter routing functions such that, 5 < N < 50. Write all the permutation cycles for this. How will you relate the connectivity of these two networks? With the help of the above permutation cycles prove this relation.

- **2C.** Design a Multistage Network that has 4, 2x2 switch boxes in each stage and uses Inverse Perfect Shuffle function between the stages. The PEs are directly connected to the switch boxes at the input side. Solve the routing functions by considering all the PEs and write the corresponding permutation cycles. Show the switch settings in the above design for routing a message from node PE<sub>5</sub> to node PE<sub>4</sub>. Find another source and destination which creates a block in the above path in the output side of middle stage. Show the switch settings for this in the same design.

- **3A.** Write an algorithm/pseudocode for calculation of the following:  $S(K) = \prod_{i=0}^{k} A_i \text{ for k=0,1,2,....,N-1 for N elements in vector A and same number of PEs in SIMD machine using <math>\log_2 N$  steps.

- **3B.** Draw a neat diagram of an Intel X86 multicore product that uses superscalar cores. Explain all the components that are shared by each core in this product.

- **3C.** Explain the organizational changes involved in processor design to increase instructional level parallelism. What are the advantages of a shared L2 cache on the chip over dedicated caches in multicore products?

- **4A.** With the help relevant diagrams, justify the following:

(i) Does write policy/policies result in inconsistency of the data?

- (ii) Does multiprocessing yield a greater performance when compared with multiprogramming?

- **4B.** With a neat diagram for each, explain the variations IA-64 processor that has a capability to issue **3M** four instructions per cycle.

- **4C.** Explain the functionalities that a multiprocessor operating system must provide so that a user can construct applications without knowing whether a single processor or multiple processors are available to handle the work submitted.

- **5A.** Explain in detail the component that has replaced front side bus in intel X86 product that uses shared L3 cache.

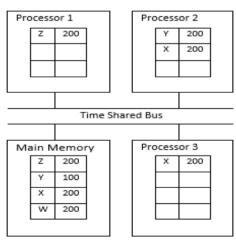

- **5B.** There are 3 processors in a multiprocessor system as shown in the figure 5B. Explain steps followed in the requesting processor and the snooping processor that uses write-invalidate protocol for the scenario given below which is executed in sequence. Draw the state transition diagram for both cases.

- i) Processor 1 wants to write to X in its cache.

- ii) Processor 3 reads the value X and Z in its cache.

Figure 5B

**5C.** Explain the blade server architecture and the ethernet configuration for a blade server site.

CSE 3101 Page 2 of 2

3M

**3M**

**2M**