## **Question Paper**

Exam Date & Time: 14-Nov-2019 (02:00 PM - 05:00 PM)

## MANIPAL ACADEMY OF HIGHER EDUCATION

INTERNATIONAL CENTRE FOR APPLIED SCIENCES END SEMESTER THEORY EXAMINATIONS NOVEMBER2019 III SEMESTER B.sc. (Applied Sciences) in Engg. ANALOG ELECTRONIC CIRCUITS [IEC 231]

Marks: 100

Answer 5 out of 8 questions. Missing data may be suitably assumed.

- 1) (5) Draw and explain the circuit diagram of common base configuration using NPN transistor. Plot the input and output characteristics. Indicate cut-off, saturation and A) active regions.

- (5) B) The dc common base current gain for a certain transistor is,  $\alpha_{dc} = 0.998$  Determine the emitter current I<sub>E</sub> if the base current is  $B=40\mu A$ . Assume that the reverse saturation current,  $I_{CBO}=2\mu A$  Also determine  $I_{CEO}$ .

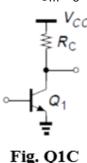

- C) (5) Draw the small signal equivalent of the CE amplifier shown in fig. Q1C. Obtain expressions for g<sub>m</sub> ,r<sub>e</sub> . and output resistance of the amplifier from the model.

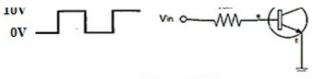

D) (5) For the transistor (Silicon) circuit shown in fig. Q1D,  $R_{n=}$  100K $\Omega$ ,  $R_{L}$ =820 $\Omega$  and  $V_{CC}$ =10V Assume  $V_{BE}$ , sat=0.8V and  $V_{CE}$ , sat=0.2V. Find the minimum base and collector current required in order to keep the transistor in saturation. Neglect I<sub>CBO</sub>. Explain briefly the working of the circuit and draw the output waveform.

Duration: 180 mins.

Fig. Q1D

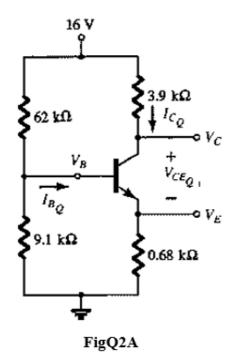

<sup>2)</sup> Determine I<sub>B</sub>, I<sub>C</sub>, I<sub>E</sub>, V<sub>CE</sub>, V<sub>B</sub>, V<sub>C</sub> and V<sub>E</sub> for the voltage divider configuration shown in <sup>(10)</sup> A) Fig Q2A given that  $\beta$ =80. Assume V<sub>BE</sub>=0.7V. What is the region of operation? Neglect I<sub>CO</sub>.

- B) Draw the circuit diagram of RC coupled amplifier with feedback using NPN transistor. <sup>(5)</sup> Mention the function of each component. Explain the working at low, medium and high frequencies.

- <sup>C)</sup> Plot the frequency response of RC coupled amplifier with and without feedback. (5) Indicate the salient features on the plot. In a 3-stage RC coupled amplifier, if the individual stage voltage gains are:A<sub>1</sub>=50dB, A<sub>2</sub>=0dB and A<sub>3</sub>=10dB respectively, find the output voltage at each stage and overall gain in decibels if the input voltage applied is Vi=10sin( $2\pi ft$ ) millivolts.

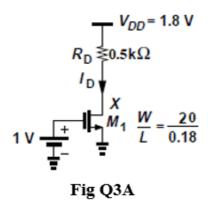

3)

(5)

A)

For the circuit in Fig. Q3A,  $\mu_n C_{ox} = 100 \ \mu A/V^2$  and  $V_{TH} = 0.4V$ . Calculate

- i) Drain current.

- ii) If the gate voltage increases by 20 mV, what is the change in the drain voltage?

- iii) What choice of R<sub>D</sub> places the transistor at the edge of the triode region with value of I<sub>D</sub> as in part <u>i</u>)?

- iv) Determine the value of W/L that places M<sub>1</sub> at the edge of saturation with V<sub>GS</sub> as in part i).

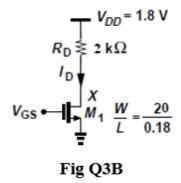

B)

Calculate the maximum allowable gate voltage in **Fig. Q3B**, if M<sub>1</sub> must remain (5) saturated. Assume  $\mu_n C_{ox} = 100 \ \mu \text{A/V}^2$  and  $V_{TH} = 0.4V$

C)

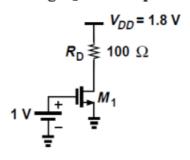

If  $\lambda = 0.1 / V$ ,  $\mu_n C_{ox} = 100 \ \mu A/V^2$ ,  $V_{TH}=0.4V$  and  $W/L = \frac{10}{0.18}$ , construct the small-signal model of the circuit shown in **Fig. Q3C.** Compute  $V_{DS} g_m$  and  $r_o$

(5)

D)

An NMOS device with  $\lambda = 0.1/V$  must provide a gain of 25 with  $V_{DS} = 1$  V. Determine the required value of W/L, if  $I_D = 1$  mA and  $\mu_n C_{ox} = 100 \ \mu A/V^2$

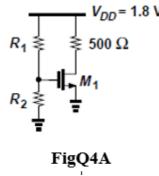

<sup>4)</sup> Design a circuit of **Fig. Q4A** for a drain current of 1 mA. If  $W/L = \frac{10}{0.18}, \mu_n C_{ox} =$  <sup>(5)</sup>

<sup>A)</sup> 100  $\mu$ A/V<sup>2</sup>,  $V_{TH} = 0.4V$ . Compute R1 and R2 such that the input impedance is at least 50 k. $\Omega$

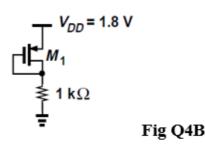

B)

If  $W/L = \frac{20}{0.18}$ ,  $\mu_p C_{ox} = 200 \ \mu \text{A/V}^2$  and  $\lambda = 0$ , determine  $V_{\text{GS}}$ ,  $V_{\text{DS}}$  and  $I_{\text{D}}$  for the circuit shown in **Fig. Q4B**. Draw the small signal model.

C)

The CS stage of **Fig. Q4C** must provide a voltage gain of 10 with a bias current of 1 mA. Assume  $\lambda_1 = \frac{0.2}{V}$ , and  $\lambda_2 = \frac{0.25}{V}$ ,  $\mu_n C_{ox} = 100 \,\mu\text{A/V}^2$ ,  $\mu_p C_{ox} = 50 \,\mu\text{A/V}^2 \,\text{V}_{\text{TH}} = 0.4 \,\text{V}$ . (a) Compute the required value of  $(\frac{W}{L})1$ .

(b) If  $(W/L)^{2=10}/0.18$ , calculate the required value of V<sub>b</sub>.

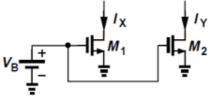

<sup>D)</sup> In the circuit of **Fig. Q4D**, M<sub>1</sub> and M<sub>2</sub> have lengths equal to 0.2  $\mu$ m,  $\mu_n C_{ox} = 100 \mu$ A/V<sup>2 (5)</sup> <u>W</u> = 0.4W and  $\lambda = 0.2$ /. Determine W<sub>2</sub> and W<sub>2</sub> such that I<sub>2</sub> = 2I<sub>2</sub> = 2 m Å Assume V<sub>Page #4</sub>

(5)

(5)

$v_{TH} = 0.4v$ , and h = -/V. Determine  $w_1$  and  $w_2$  such that  $i_X = 2i_Y = 2$  mA. Assume  $v_{DS1} = V_{DS2} = V_B = 1V$ . What is the output resistance of each current source?

Fig Q4D

- <sup>5)</sup> State Barkhausen criteria for sustained oscillations. Draw the circuit diagram of Hartley <sup>(5)</sup> oscillator and explain its working. Write the expression for frequency of oscillations

- A)

- B) With the help of a circuit diagram, explain the working of transformer coupled Class B <sup>(5)</sup> push pull power amplifier. Derive an expression for the maximum power efficiency. Mention one drawback of this amplifier.

- <sup>C)</sup> With the help of a block diagram, explain positive feedback. Derive an expression for <sup>(5)</sup> gain in a positive feedback amplifier. Mention the application of positive feedback.

- D) State and explain Millers theorem with an illustration. Explain any one application of (5) this theorem with necessary circuit

- <sup>6)</sup> Draw the circuit diagram of High Frequency Model of MOSFET and explain. Write the <sup>(5)</sup> expressions for the cutoff frequencies on the input and output side of the amplifier.

- A)

- <sup>B)</sup> In an RC phase shift oscillator using FET, the value of resistors and capacitors in the <sup>(5)</sup> feedback circuit are R = 150 K $\Omega$  and C = 0.25 Nano Farads. Determine the frequency of oscillation. If the value of R<sub>D</sub> =1k $\Omega$  and g<sub>m</sub> = 2500millimhos, find the gain of the amplifier.

- <sup>C)</sup> With suitable diagrams, explain how power amplifiers are classified based on the <sup>(5)</sup> operating point.

- <sup>D)</sup> Determine the voltage gain, input and output impedance with feedback for voltage Series <sup>(5)</sup> feedback having A= -100,  $R_i = 10k\Omega$  and  $R_o = 20k\Omega$  for feedback of i)  $\beta = -0.1$  ii)  $\beta = -0.5$

- <sup>7)</sup> Draw the block schematic of i) Voltage shunt ii) Current series feedback amplifiers. <sup>(5)</sup>

<sup>(5)</sup> What is the effect of series and shunt feedback on the input and output resistance of an amplifier?

- B) Draw the circuit diagram of a crystal oscillator and explain the working. Mention any <sup>(5)</sup> two advantages of Crystal oscillators.

- C) Explain the construction, working and characteristics of MOSFET. Sketch output and <sup>(5)</sup> transfer characteristics.

- D) With necessary current equation explain Triode and Saturation region in MOSFET. (5)

Explain how current varies when width, length is varied with necessary plot.

- <sup>8)</sup> Explain the following:

- i) Early effect in BJT

- ii) Channel length modulation in MOSFET

(20)

iii) Advantages and disadvantages of Positive and Negative feedback

iv) Piezoelectric effect in crystals (5X4=20)

-----End-----