## **Question Paper**

Exam Date & Time: 28-Dec-2019 (09:30 AM - 12:30 PM)

## MANIPAL ACADEMY OF HIGHER EDUCATION

INTERNATIONAL CENTRE FOR APPLIED SCIENCES END SEMESTER THEORY EXAMINATIONS NOVEMBER 2019 III SEMESTER B.sc. (Applied Sciences) in Engg. SWITCHING CIRCUITS AND LOGIC DESIGN [ICS 232]

Marks: 100

## Answer 5 out of 8 questions.

| 1) | A) | Simplify the following expressions using algebraic manipulation.<br>i) $F(A, B, C, D) = \sum m (3, 7, 9, 12, 13, 14, 15)$<br>ii) $f(a, b, c, d, e)=a'c'e'+a'c'd'+a'de+ab'c'e$<br>iii) $F(A, B, C,D)=(A'+C'+D')(B'+C'+D)(A+B'+C')$<br>iv) $F(A, B, C)=\prod M (0, 1, 5)$<br>(4X3=12)                                                                                                                                      | (12) |

|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | В) | i) Derive the minimum cost SOP expression for the following function using K-map and implement using only NOR gates. Write all prime implicants and Essential prime implicants.<br>F(a, b, c, d)= $\sum m(0, 1, 2, 5, 7, 8, 10, 12, 14, 15)$<br>ii) Find the minimum cost SOP and POS expression for the following function using K-map.<br>F(w, x, y, z)= $\sum m(0, 1, 3, 4, 7, 11, 13, 15) + d(9, 12, 14)$<br>(5+3=8) | (8)  |

| 2) | A) | A circuit with two outputs has to implement the following functions $f(x1, x2, x3, x4)=\sum m(0, 2, 4, 6, 7, 9) + d(10,11)$<br>$g(x1, x2, x3, x4)=\sum m(2, 4, 9, 10, 15) + d(0, 13, 14)$<br>Implement it and compare its cost with combined costs of two SOP implementations that implement f and g separately. Assume that the input variables are available in both complemented and complemented forms.              | (10) |

|    | В) | <ul> <li>i) Perform 2's complement addition for the following :</li> <li>a) (+5) + (+2) b) (-5) + (+2) c) (+5) + (-2) d) (-5) + (-2)</li> <li>ii) Design and write the behavioral Verilog code for 4-bit adder/subtractor unit.</li> <li>(4+6=10)</li> </ul>                                                                                                                                                             | (10) |

| 3) | A) | i) Design a single-digit BCD adder.<br>ii) Design and write Verilog code to convert BCD to excess-3 code using a<br>four-bit adder.<br><b>(3+7=10)</b>                                                                                                                                                                                                                                                                   | (10) |

|    | В) | Design a BCD to 2421 code converter using 8:1 MUXes. Write Verilog code to implement this.                                                                                                                                                                                                                                                                                                                               | (10) |

Duration: 180 mins.

| 4) | A) | <ul> <li>i) Write behavioral Verilog code to convert an N bit binary number into equivalent gray code. Use for loop.</li> <li>ii) write the truth table and circuit diagram for 4-to-1 Multiplexer.</li> <li>iii) write the truth table and circuit diagram for three-input majority function using 4-to-1 multiplexer.</li> <li>(3X3=9)</li> </ul>                                                                                                                                                                                                  | (9)  |

|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | В) | i) Write the truth table for 3-to-8 decoder and design 3-to-8 decoder using two 2-to-4 decoders.<br>ii) Design and Write Verilog code to implement f (A, B, C) = $\Sigma m$ (0, 2, 3, 4, 5, 7) using 3 to 8 binary decoder and an OR gate. Use case statement.<br>(5+6=11)                                                                                                                                                                                                                                                                           | (11) |

| 5) | A) | <ul> <li>i) Write the truth table for 4-to-2 priority encoder with active high enable and active low output.</li> <li>ii) write Verilog code for 8:1 multiplexer using two 2-to-4 decoders and external gates. Implement the 2-to-4 decoder module using for loop. (3+8=11)</li> </ul>                                                                                                                                                                                                                                                               | (11) |

|    | В) | i) Design a 4-bit comparator circuit using full adders. The inputs to the comparator are A=a3a2a1a0 and B=b3b2b1b0. The output is AeqB, which is high when A=b and low when A!=B.<br>ii) A combinational circuit building block receives an 8 bit input A7-0, and produces a 3 bit output Y2-0 and one 1 bit output Z. Y indicates the most significant line number of the input that is TRUE. Z should be TRUE if there are one or more TRUE bits on the input. What is this building block? Draw the block diagram and the truth table.<br>(3+6=9) | (9)  |

| 6) | A) | i) Draw the logic diagram of D flip flop. Write its characteristic table,<br>characteristic equation, and excitation table.<br>ii) With neat diagram explain the working of D type positive edge triggered                                                                                                                                                                                                                                                                                                                                           | (12) |

- II) vvitr at diagram explain the working of D type positive edge triggered Flip-Flop. (6+6=12)

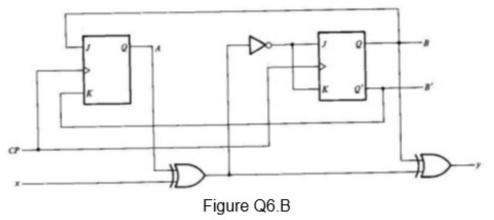

- B) The logic diagram of a sequential circuit is given in Figure Q6.B. Derive the <sup>(8)</sup> state table and state diagram of the circuit.

(10) Design a counter with the following repeated nonbinary sequence: 0, 1, 2, 3, 4, 5, 6. Use JK flip-flops. Treat the unused states as a don't-care A)

7)

conditions.

B)

8)

i. Design a 4-bit bi-directional shift register for the following operations using <sup>(10)</sup> D flip flops and MUXs.

| Shift | Load | Operation          |

|-------|------|--------------------|

| 0     | 0    | No change          |

| 0     | 1    | Load parallel data |

| 1     | d    | Shift right        |

ii. Design and write the Verilog code for 4-bit asynchronous up counter using T Flip-Flop.(4+6=10)

A) Explain the following with a neat diagram for each. (12)

i) NMOS realization of a NAND gate.

ii) NMOS realization of a NOR gate.

iii) CMOS realization of a NAND gate.

iv) CMOS realization of a NOR gate.

(4X3=12)

B) i) Discuss PLA with a neat logic diagram.

ii) Define a tri-state buffer. Write its truth table.

(6+2=8)

-----End-----