Reg. No.

## VII SEMESTER B.TECH (ELECTRICAL & ELECTRONICS ENGINEERING) END SEMESTER EXAMINATIONS, NOVEMBER 2019

## **MODERN POWER CONVERTERS [ELE 4010]**

**REVISED CREDIT SYSTEM**

| REVISED CREDIT SYSTEM       |                                                                                                                                                                                                                                                                                                                                                                           |              |  |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|

| Time                        | e: 3 Hours Date: 21 November 2019 Ma                                                                                                                                                                                                                                                                                                                                      | x. Marks: 50 |  |  |  |  |

| Instructions to Candidates: |                                                                                                                                                                                                                                                                                                                                                                           |              |  |  |  |  |

|                             | <ul> <li>Answer ALL the questions.</li> </ul>                                                                                                                                                                                                                                                                                                                             |              |  |  |  |  |

|                             | <ul> <li>Missing data may be suitably assumed.</li> </ul>                                                                                                                                                                                                                                                                                                                 |              |  |  |  |  |

| 1A.                         | Consider a buck converter with the following specifications: $V_g = 8$ R = 18 $\Omega$ , P <sub>o</sub> = 100 W, L = 0.4 mH and f <sub>s</sub> =150 kHz. (a) Determine the m of operation. (b) Determine the value of R for the converter so as to p the operation to continuous (in case of discontinuous mode) discontinuous (in case of continuous mode) current mode. | node<br>oush |  |  |  |  |

| 1B.                         | Design a boost converter that will have an output of 25 V from a 9 V sou<br>The load resistance is 50 $\Omega$ . Assume ideal components and continuous m<br>of operation. Maintain output voltage ripples less than 1% and cur<br>ripples to be 10% of average inductor current. Take f <sub>s</sub> = 25 kHz.                                                           | node         |  |  |  |  |

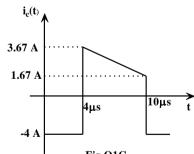

| 1C.                         | The capacitor current of a buck-boost converter is shown in Fig.(<br>Determine duty ratio, maximum inductor current, minimum indu<br>current, average source current and average diode current.                                                                                                                                                                           |              |  |  |  |  |

| 2A.                         | With a help of a neat circuit schematic and principle of volt second bala<br>amp second balance, derive the relationship between the output voltage<br>the supply voltage for a SEPIC. Hence, deduce an expression of the<br>inductor in terms of supply voltage, duty cycle and current ripple.                                                                          | and          |  |  |  |  |

| 2B.                         | A flyback dc-dc converter has an input voltage of 44 V and an output vol<br>of 3 V. The duty ratio is fixed at 0.32 and the switching frequence<br>300 kHz. The load is 1 $\Omega$ . (a) Determine the transformer turns ratio.<br>Determine the transformer magnetizing inductance such that the minin<br>inductor current is 40% of the average inductor current.       | cy is<br>(b) |  |  |  |  |

| 2C.                         | A full bridge dc-dc converter has the following specifications: $V_g = 3 N_p/N_s = 2$ , D = 0.3, L = 0.5 mH, R = 6 $\Omega$ , C = 50 $\mu$ F and $f_s = 10$ Determine average output voltage, minimum value of inductor current the percentage output voltage ripple. Assume all components to be idea                                                                    | kHz.<br>and  |  |  |  |  |

| 3A.                         | Explain the role of tertiary winding in case of Forward converter. He derive an expression for the duty ratio D which ensures the demagnetization of the core before the start of next switching cycle.                                                                                                                                                                   |              |  |  |  |  |

| 3B.                         | The Zero Current Switch buck resonant converter has following parameter $V_g = 100V$ , $I_o = 1.5A$ , $L_r = 10\mu$ H, $C_r = 0.01\mu$ F and $f_s = 50$ kHz. Determine output voltage of converter.                                                                                                                                                                       |              |  |  |  |  |

- **3C.** In a SLR dc-dc converter,  $V_g = 100$  V,  $L_r = 75$  µH,  $C_r = 0.04$  µF,  $f_s = 100$  kHz, R = 10  $\Omega$ . (a) Determine the output voltage V<sub>o</sub>. (b) If the source voltage now varies over ±5%, find the range of switching frequency necessary to regulate the output voltage.

- **4A.** With suitable block schematic, show that negative feedback results in reduction of transfer functions of the converter.

- **4B.** Discuss in detail the basic constraints for the design of a high frequency inductor when the core geometrical factor  $K_g$  method is employed for the design.

- **4C.** The Parallel loaded Resonant dc dc converter has following parameters:  $V_g = 15 V$ ,  $L_r = 1.3 \mu$ H,  $C_r = 0.12 \mu$ F,  $R = 10 \Omega$ ,  $f_s = 500 k$ Hz. Determine output voltage of the converter. Estimate the new output voltage if the load resistance is changed to 5  $\Omega$ .

- **5A.** A filter inductor is to be designed for the following specifications: Inductance  $L = 50 \mu$ H, peak current  $I_{max} = 11$  A, RMS current  $I_{rms} = 10$  A, maximum allowed power loss  $P_{max} = 2$  W. The ferrite core material available for this design has a saturation flux density  $B_{sat} = 0.4$  T, but engineering margin requires that the maximum flux density  $B_{max}$  should not exceed 0.3 T. The cores that can be used in this design are listed in Table Q5A.1. The copper wires that can be used in this design are listed in Table 5A.2. The inductor winding is expected to reach a temperature of 100°C, so the appropriate resistivity of copper p is 2.3 x 10-8  $\Omega$ -cm. Assuming the fill factor K<sub>u</sub> of the core as 0.5, core loss and skin and proximity effect to be neglected, select the smallest core whose K<sub>g</sub> satisfies the design requirement. Also, determine the required length of the air gap, number of turns and an appropriate wire for this inductor.

- **5B.** Assuming ideal components and continuous conduction mode, develop the small-signal ac equivalent circuit model of a buck-boost converter.

- **5C.** For the small-signal model of the buck-boost converter developed in Q 5B, derive the open loop control to output transfer function. Represent your answer in the standard form.

|             |                          |              | •            | Fig.Q1C      |

|-------------|--------------------------|--------------|--------------|--------------|

| <u>Core</u> | $\underline{K}_{g}$      | <u>A</u> c   | <u>W</u> A   | <u>(MLT)</u> |

| <u>#</u>    | <u>(m<sup>5</sup>)</u>   | <u>(cm²)</u> | <u>(cm²)</u> | <u>(cm)</u>  |

| 1           | 2.2 x 10 <sup>-12</sup>  | 0.62         | 0.256        | 4.4          |

| 2           | 3.4 x 10 <sup>-12</sup>  | 0.62         | 0.384        | 4.4          |

| 3           | 8.4 x 10 <sup>-12</sup>  | 1.19         | 0.333        | 5.62         |

| 4           | 12.5 x 10 <sup>-12</sup> | 1.18         | 0.503        | 5.62         |

| 5           | 20.3 x 10 <sup>-12</sup> | 1.7          | 0.471        | 6.71         |

| 6           | 38.4 x 10 <sup>-12</sup> | 1.61         | 0.995        | 6.71         |

| 7           | 82.2 x 10 <sup>-12</sup> | 1.96         | 1.61         | 7.52         |

| 8           | 120 x 10 <sup>-12</sup>  | 2.01         | 2.5          | 8.39         |

Table Q5A.1

| AWG      | Aw                       |  |  |  |  |

|----------|--------------------------|--|--|--|--|

| <u>#</u> | <u>(cm²)</u>             |  |  |  |  |

| 14       | 20.02 x 10 <sup>-3</sup> |  |  |  |  |

| 15       | 16.51 x 10 <sup>-3</sup> |  |  |  |  |

| 16       | 13.07 x 10 <sup>-3</sup> |  |  |  |  |

| 17       | 10.39 x 10 <sup>-3</sup> |  |  |  |  |

| 18       | 8.23 x 10 <sup>-3</sup>  |  |  |  |  |

| 19       | 6.53 x 10 <sup>-3</sup>  |  |  |  |  |

| 20       | 5.19 x 10 <sup>-3</sup>  |  |  |  |  |

| 21       | 41.2 x 10 <sup>-3</sup>  |  |  |  |  |

|          |                          |  |  |  |  |

Table Q5A.2

Page 2 of 2

(04)

(04)

(02)

(04)

(04)

(04)

(02)

( **.** . .