#### DEPARTMENT OF MECHATRONICS III SEMESTER B. TECH MECHATRONICS END SEM EXAM

Subject: Digital System Design Time: 45 Min + 3 Min

#### Subject Code: MTE 2152 Date: 24/1/2022

### Part-A

# Note: All Questions carry equal mark (One mark each). All questions are compulsory and there is No negative marking for wrong answer.

|          | answer.                                                                                                                                                                                                                                                      |   |    |    |        |        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|--------|--------|

| Q.<br>No |                                                                                                                                                                                                                                                              | M | СО | РО | L<br>O | B<br>L |

| 1.       | Which gate is a basic logic gate?<br>a. XOR Gate                                                                                                                                                                                                             | 1 | 1  | 1  | 1      | 2      |

|          | <ul><li>b. NOT Gate</li><li>c. NAND Gate</li><li>d. NOR Gate</li></ul>                                                                                                                                                                                       |   |    |    |        |        |

| 2        | De Morgan's Law states that<br>a. $A^{+}B^{-}=AB^{-}A^{-}+B^{-}=AB^{-}$<br>b.<br>c. $AB^{-}AB^{-}$<br>d. =<br>e. $A^{-}A^{-}$<br>f. $BB$<br>g.<br>h. $AB^{-}AB^{-}$<br>i. =<br>j. $A^{-}A^{-}$<br>k. +<br>l. $BB$<br>m.<br>n. $AB^{-}AB^{-}$<br>o. = $A + B$ | 1 | 1  | 1  | 1      | 1      |

| 3        | In negative logic<br>a. 1-high, 0-low<br>b. 0-high, 1-low<br>c. 1-high, 1-low<br>d. 0-high, 0-low                                                                                                                                                            | 1 | 1  | 1  | 1      | 1      |

| 4  | Convert the binary number $1111.0010_2$ to decimal. | 1 | 1 | 3 | 1 | 1 |

|----|-----------------------------------------------------|---|---|---|---|---|

|    |                                                     | 1 |   |   |   |   |

|    | a. 115.125                                          |   |   |   |   |   |

|    | b. 15.125                                           |   |   |   |   |   |

|    | c. 15<br>d. 1.5                                     |   |   |   |   |   |

|    | d. 1.5                                              |   |   |   |   |   |

| 5  | 2's complement representation of -17 is             | 1 | 2 | 1 | 1 | 2 |

|    | a. 101110                                           |   |   |   |   |   |

|    | b. 101111                                           |   |   |   |   |   |

|    | c. 111110                                           |   |   |   |   |   |

|    | d. 110001                                           |   |   |   |   |   |

| 6  | Decimal 43 in hexadecimal and BCD number            | 1 | 2 | 1 | 1 | 1 |

|    | system is respectively.                             |   |   |   |   |   |

|    | a. B2, 0100 0011                                    |   |   |   |   |   |

|    | b. 2B, 0100 0011                                    |   |   |   |   |   |

|    | c. 2B, 0011 0100                                    |   |   |   |   |   |

|    | d. B2, 0100 0100                                    |   |   |   |   |   |

| 7. | Convert binary number (1101) into gray code:        | 1 | 2 | 1 | 1 | 1 |

|    | a. 1000                                             |   |   |   |   |   |

|    | b. 1100                                             |   |   |   |   |   |

|    | c. 1010                                             |   |   |   |   |   |

|    | d. 1011                                             |   |   |   |   |   |

| 8. | 11001, 1001 and 111001 corresponds to the 2's       | 1 | 1 | 1 | 1 | 2 |

|    | complement representation of which one of the       |   |   |   |   |   |

|    | following sets of numbers?                          |   |   |   |   |   |

|    | a. 25, 9 and 57 respectively                        |   |   |   |   |   |

|    | b6, -6 and -6 respectively                          |   |   |   |   |   |

|    | c7, -7 and -7 respectively                          |   |   |   |   |   |

|    | d25, -9 and -57 respectively                        |   |   |   |   |   |

| 9. | K-map for a Boolean function is shown in figure.    | 1 | 1 | 1 | 1 | 2 |

|    | The number of essential prime implicants for this   |   |   |   |   |   |

|    | function is                                         |   |   |   |   |   |

|    |                                                     |   |   |   |   |   |

|     | AB                                               |   |   |   |   |   |

|-----|--------------------------------------------------|---|---|---|---|---|

|     | CD 00 01 11 10                                   |   |   |   |   |   |

|     | 00 1 1 0 1                                       |   |   |   |   |   |

|     | 01 0 0 0 1                                       |   |   |   |   |   |

|     |                                                  |   |   |   |   |   |

|     |                                                  |   |   |   |   |   |

|     |                                                  |   |   |   |   |   |

|     | a. 4                                             |   |   |   |   |   |

|     | b. 5                                             |   |   |   |   |   |

|     | c. 6<br>d. 81                                    |   |   |   |   |   |

| 10. | The logic expression                             | 1 | 1 | 3 | 1 | 3 |

| 10. | Y=A+A-B Y=A+A-B                                  | 1 | 1 | 5 | T | 5 |

|     | is equivalent to                                 |   |   |   |   |   |

|     | a.<br>h y adv <i>ad</i>                          |   |   |   |   |   |

|     | b. $Y=AB Y=AB$<br>c.                             |   |   |   |   |   |

|     | d. $Y = A - B Y = A - B$                         |   |   |   |   |   |

|     | е.                                               |   |   |   |   |   |

|     | f. $Y=A-+BY=A-+B$                                |   |   |   |   |   |

|     | g. $V \to D K - 4 / B$                           |   |   |   |   |   |

|     | h. $Y=A+BY=A+B$<br>i.                            |   |   |   |   |   |

| 11. | In half adder carry output is high if inputs are | 1 | 1 | 1 | 1 | 2 |

|     | a. 0,0                                           |   |   |   |   |   |

|     | b. 1,1                                           |   |   |   |   |   |

|     | c. 1,0<br>d. 0.1                                 |   |   |   |   |   |

|     | d. 0,1                                           |   | 1 |   | 1 |   |

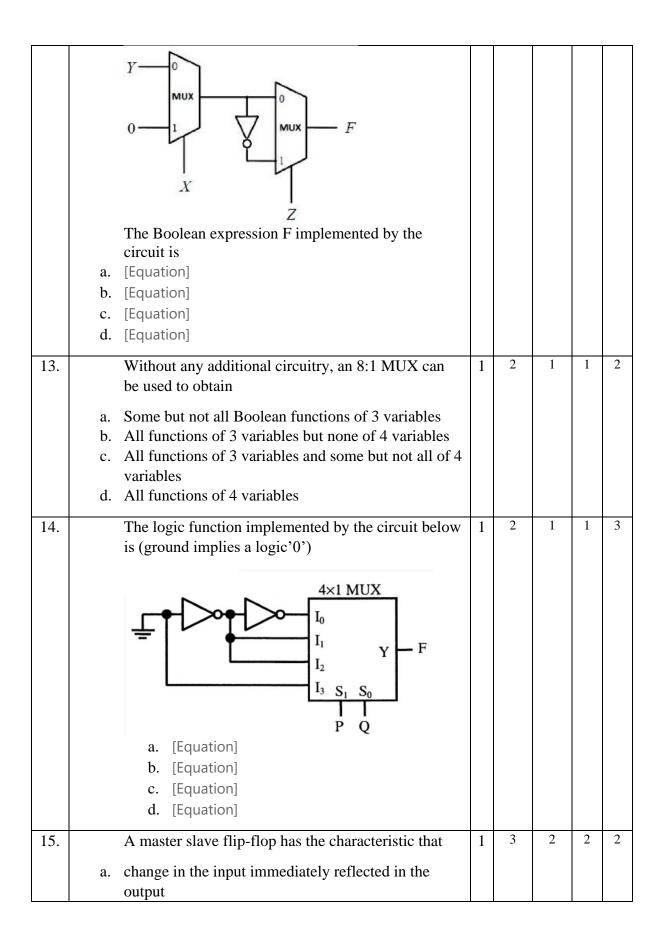

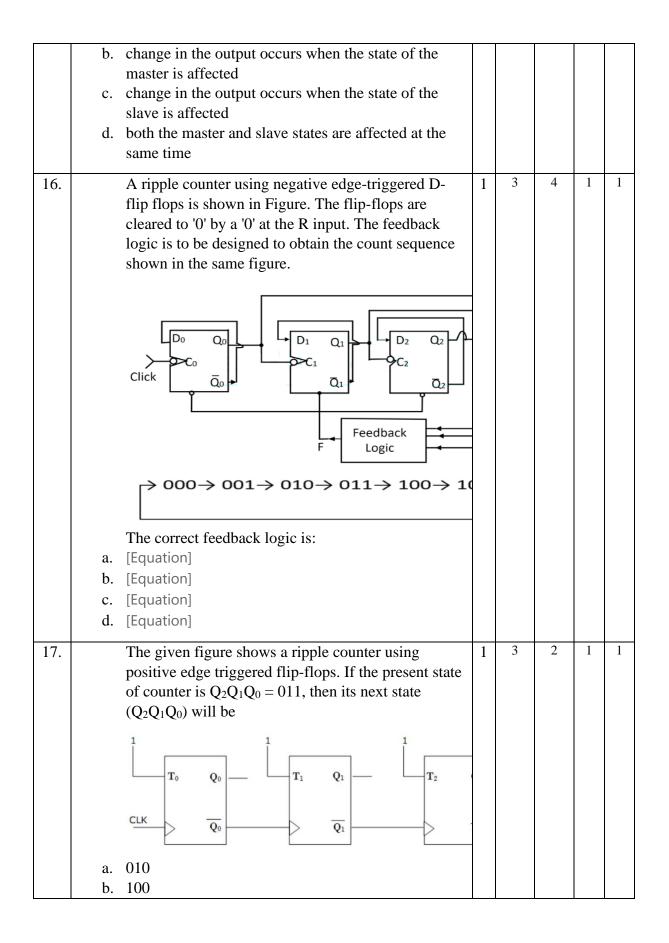

| 12. | Consider the circuit shown in the figure.        | 1 | 1 | 3 | 1 | 3 |

|     |          | 111                                                   |   |   |   |   |   |

|-----|----------|-------------------------------------------------------|---|---|---|---|---|

|     |          |                                                       |   |   |   |   |   |

|     | d.       | 101                                                   |   |   |   |   |   |

| 18. |          | Unused states are treated as Don't cares conditions   | 1 | 1 | 1 | 1 | 1 |

|     |          | during the                                            |   |   |   |   |   |

|     |          |                                                       |   |   |   |   |   |

|     | a.       | Design of a circuit                                   |   |   |   |   |   |

|     | b.       | Execution                                             |   |   |   |   |   |

|     | c.       | Pulse trigger                                         |   |   |   |   |   |

|     | d.       | Edge trigger                                          |   |   |   |   |   |

| 19. |          | Memory elements in clocked sequential circuits are    | 1 | 2 | 1 | 1 | 1 |

|     |          | called                                                |   |   |   |   |   |

|     |          |                                                       |   |   |   |   |   |

|     | a.       | Latches                                               |   |   |   |   |   |

|     | b.       | Flip-flop                                             |   |   |   |   |   |

|     | с.       | Signals                                               |   |   |   |   |   |

|     | d.       | Gates                                                 |   |   |   |   |   |

| 20. |          | A counter that flows the binary sequence is called    | 1 | 3 | 3 | 2 | 1 |

|     |          |                                                       |   |   |   |   |   |

|     |          | Ripple counter                                        |   |   |   |   |   |

|     | f.       | Edge counter                                          |   |   |   |   |   |

|     | g.       | Binary counter                                        |   |   |   |   |   |

|     | h.       | Level counter                                         |   |   |   |   |   |

| 21. |          | Which of the follwing is not a sequential circuit?    | 1 | 3 | 2 | 1 | 1 |

|     | a.       | Flip-flop                                             |   |   |   |   |   |

|     | b.       | Counter                                               |   |   |   |   |   |

|     | с.       | Shift register                                        |   |   |   |   |   |

|     | d.       | Multiplexer                                           |   |   |   |   |   |

|     |          |                                                       |   |   |   |   |   |

| 22. |          | The negative transition in flip-flops are reffered to | 1 | 3 | 2 | 1 | 1 |

|     |          | as                                                    |   |   |   |   |   |

|     | a.       | Clock                                                 |   |   |   |   |   |

|     | a.<br>b. | Negative edge                                         |   |   |   |   |   |

|     | c.       | Positive edge                                         |   |   |   |   |   |

|     | d.       | Pulse transition                                      |   |   |   |   |   |

|     | u.       |                                                       |   |   |   |   |   |

| 23. |          | The full form of PIPO is                              | 1 | 3 | 2 | 1 | 1 |

|     | a.       | Parallel-in Peripheral-out                            |   |   |   |   |   |

|     | b.       | Parallel-in Parallel-out                              |   |   |   |   |   |

|     | с.       | Peripheral-in Parallel-out                            |   |   |   |   |   |

|     | d.       | Peripheral -In Peripheral-Out                         |   |   |   |   |   |

|     | l        |                                                       |   |   |   |   |   |

| 24. | How many test patterns are required to test the circuit using counters?                | ne 1     | 3 | 2 | 1 | 1 |

|-----|----------------------------------------------------------------------------------------|----------|---|---|---|---|

|     | a. 2 <sup>n</sup>                                                                      |          |   |   |   |   |

|     | (n-1)                                                                                  |          |   |   |   |   |

|     |                                                                                        |          |   |   |   |   |

|     | c. $2^{n} - 1$<br>d. $2^{n} + 1$                                                       |          |   |   |   |   |

|     | d. $2^{-} + 1$                                                                         |          |   |   |   |   |

| 25. | What happens if the input is low in FSM?                                               | 1        | 3 | 2 | 1 | 1 |

|     | a. Change of state                                                                     |          |   |   |   |   |

|     | b. No Transition in state                                                              |          |   |   |   |   |

|     | c. Remain in a single state                                                            |          |   |   |   |   |

|     | d. Invalid state                                                                       |          |   |   |   |   |

| 26. | In the FSM Diagram, what does arrow betwe                                              | en the 1 | 3 | 2 | 1 | 1 |

| -01 | circles are represent?                                                                 |          |   |   |   |   |

|     | •                                                                                      |          |   |   |   |   |

|     | a. Change of state                                                                     |          |   |   |   |   |

|     | b. State                                                                               |          |   |   |   |   |

|     | c. Output value                                                                        |          |   |   |   |   |

|     | d. Initial state                                                                       |          |   |   |   |   |

| 27. | FPGA stands for                                                                        | 1        | 3 | 2 | 1 | 1 |

|     | a. Field Program Gate Array                                                            |          |   |   |   |   |

|     | b. First Program Gate Array                                                            |          |   |   |   |   |

|     | c. Field Programmable Gate Array                                                       |          |   |   |   |   |

|     | d. First Programmable Gate Array                                                       |          |   |   |   |   |

| 28. | Many companies are transitioning to using F                                            | PGAs 1   | 4 | 1 | 1 | 1 |

|     | for their processor designs instead of ASICs.                                          |          |   |   |   |   |

|     | a. FPGAs always outperform an ASIC.                                                    |          |   |   |   |   |

|     | b. The development cycle of the FPGA is much                                           |          |   |   |   |   |

|     | shorter.                                                                               |          |   |   |   |   |

|     | c. FPGAs are more space-efficient.                                                     |          |   |   |   |   |

|     | d. FPGAs are both smaller and faster.                                                  |          |   |   |   |   |

|     | e. None of the above.                                                                  |          |   |   |   |   |

| 29. | Most EDGA logic modules utilize a(r)                                                   | 1        | 4 | 1 | 1 | 1 |

| 29. | Most FPGA logic modules utilize a(n)<br>approach to create the desired logic functions |          | + |   |   | 1 |

|     | a. AND array                                                                           |          |   |   |   |   |

|     | b. Look-up table                                                                       |          |   |   |   |   |

|     | c. OR array                                                                            |          |   |   |   |   |

|     | d. AND and OR array                                                                    |          |   |   |   |   |

|     | ······································                                                 |          |   |   |   |   |

| 30. |    | In spartan-3 family architecture, which            | 1 | 4 | 1 | 1 | 1 |

|-----|----|----------------------------------------------------|---|---|---|---|---|

|     |    | programmable functional element accepts two 18-bit |   |   |   |   |   |

|     |    | binary numbers as inputs and computes the product? |   |   |   |   |   |

|     | a. | Configurable Logic Blocks                          |   |   |   |   |   |

|     | b. | Input Output Blocks                                |   |   |   |   |   |

|     | с. | Block RAM                                          |   |   |   |   |   |

|     | d. | Multiplier Blocks                                  |   |   |   |   |   |

|     |    |                                                    |   |   |   |   |   |

#### DEPARTMENT OF MECHATRONICS ENGINEERING III SEMESTER B. TECH (MECHATRONICS ENGINEERING)

#### END SEMESTER EXAMINATIONS PART B, JAN 2022

#### SUBJECT: DIGITAL SYSTEM DESIGN [MTE 2152]

#### **Time: 75 Min + 10 Min**

## Date: 24/1/2022

|           | Max. Marks: 20                                                                                                                                                  |   |     |                              |                     |     |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|------------------------------|---------------------|-----|--|

| Q.<br>No. |                                                                                                                                                                 | Μ | СО  | РО                           | LO                  | BL  |  |

| 1A        | Solve the given equation using VEM, to obtain the minimum SOP expression. $F(A, B, C, D, E) = \sum m(1,4,8,11,12,14,15,24,25,30) + d(6,9,13,16,17,22,23,28,29)$ | 5 | CO1 | PO1,<br>PO3,<br>PO12         | 1, 7,<br>13         | 2,3 |  |

| 1B        | Design a 4-bit 4 state ring counter with a single circulating '0' using 74194                                                                                   | 3 | CO3 | PO1,<br>PO2,<br>PO3,<br>PO12 | 3,7,<br>8,9,<br>13  | 2,3 |  |

| 1C        | Develop a MOD 14 counter using 7493 IC.                                                                                                                         | 2 | CO3 | PO1,<br>PO2,<br>PO3,<br>PO12 | 3,7,<br>8,13<br>,18 | 2,3 |  |

| 2A        | Illustrate the dataflow Verilog code for a single bit full adder. Using this as a component, develop a Verilog code for a 4-bit full adder.                     | 4 | CO5 | PO1,<br>PO5,<br>PO12         | 3,6,<br>8,9,<br>13  | 2,3 |  |

| 2B        | Demonstrate a 4 to 16 decoder, using 3 to 8 decoders.                                                                                                           | 3 | CO2 | PO1,<br>PO2,<br>PO3,<br>PO12 | 2, 7,<br>9,<br>13   | 2,3 |  |

| 2C        | Construct a JK flip flop using D flip flop                                                                                                                      | 3 | CO3 | PO1,<br>PO2,<br>PO3,<br>PO12 | 3,7,<br>8,9,<br>13  | 2,3 |  |