## **Question Paper**

Exam Date & Time: 23-Jan-2023 (09:30 AM - 12:30 PM)

### MANIPAL ACADEMY OF HIGHER EDUCATION

# THIRD SEMESTER B.TECH MAKE-UP EXAMINATIONS, JAN-FEB 2023 ANALOG ELECTRONICS [BME 2151]

Marks: 50 Duration: 180 mins.

### Answer all the questions.

#### **Instructions to Candidates:**

- (i) Answer ALL questions

- (ii) Missing data may be suitably assumed

- (iii) Draw neat diagrams wherever necessary

- 1) Devise  $R_B$  and  $R_C$  for a Silicon transistor circuit in common emitter configuration to produce  $\frac{1}{10}$  = (2) 36.36 $\mu$ A,  $V_{CEQ}$  = 14V and  $V_{CEQ}$  = 14V

A)

- B) A common emitter amplifier employing Ge transistor is biased using voltage divider bias. The various circuit parameters are  $V_{CC}$  = 16V,  $R_{C}$  = 3K $\Omega$ ,  $R_{E}$  = 2K $\Omega$ ,  $R_{1}$  = 56K $\Omega$ ,  $R_{2}$  = 20K $\Omega$  and  $\Omega$  = 0.985. Determine:

- i. Operating point

- ii. Stability factor "S"

- C) Bias an NPN transistor in fixed bias configuration and derive an expression for stability factor "S". (4)

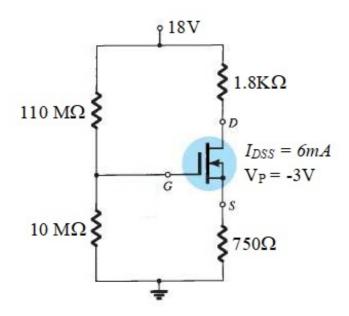

- 2) Determine  $V_{GSQ}$ ,  $I_{DQ}$  and  $V_{DSQ}$  of the following circuit using graphical analysis. (4)

A)

B) Making use of a tuned circuit with two capacitors and one inductor, how do you generate sinusoidal (3)

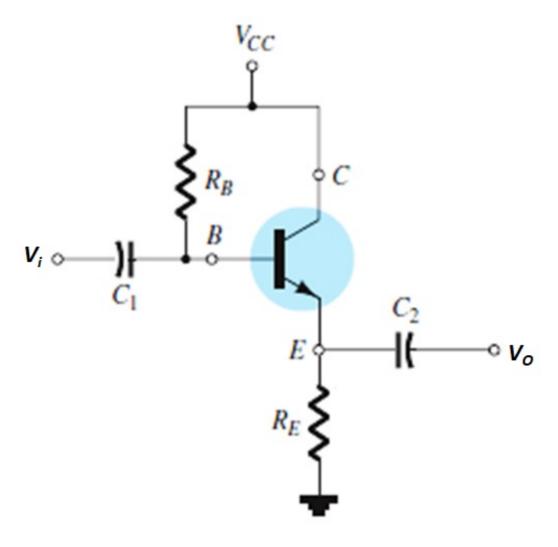

C) Draw the small signal model of the following circuit and analyse it for input and output impedances. (3)

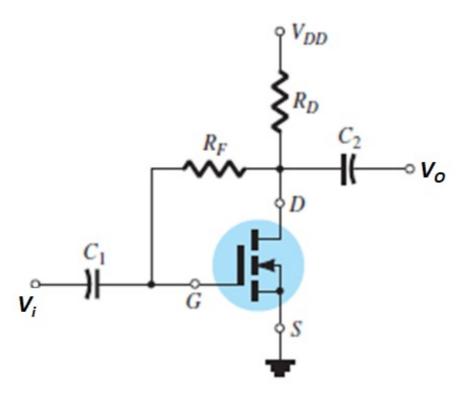

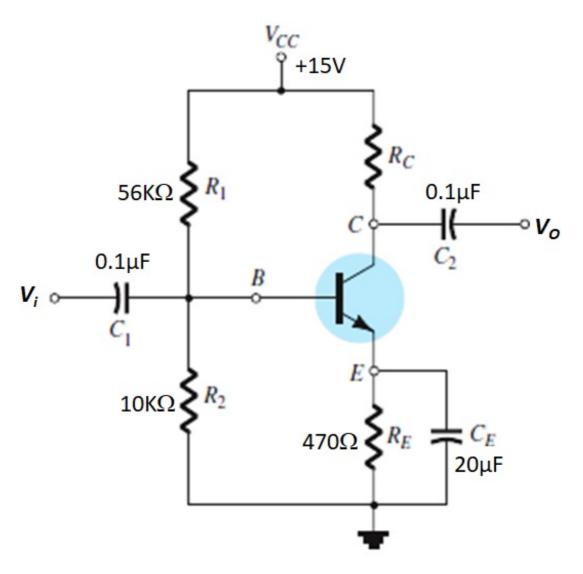

3) Develop a small signal model of the following circuit and estimate input & output impedances and voltage gain. (4)

A)

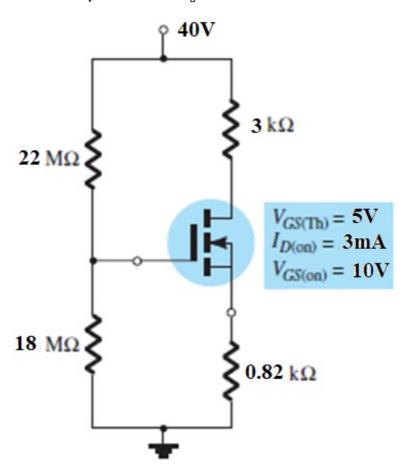

- B) For the circuit shown below, having  $I_{DQ}$  = 6.7mA and  $V_{GSQ}$  = 12.5V, and  $g_{os}$  = 20 $\mu$ S. (4)

- 1. Determine  $g_m$

- 2. Find *r<sub>d</sub>*

- 3. Calculate  $Z_i$

- 4. Find  $Z_o$  with and without  $r_d$

- 5. Find  $A_v$  with and without  $r_d$

- C) Write any two advantages and any two drawbacks of Class-A power amplifier.

- network) (4)

(2)

- 4) Draw circuit diagram and equivalent ac circuit (considering the loading effect of feedback network) (4 of a BJT based voltage-series feedback amplifier, and derive input impedance and voltage gain with feedback.

- A)

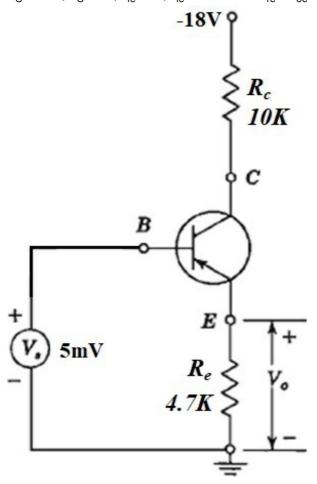

- B) Determine output voltage, input impedance and output impedance of the following circuit. Assume  $V_S = 5mV$ ,  $V_S = 0\Omega$ ,  $V_{fe} = 0$ ,  $V_{fe} = 1.1$ K $\Omega$  and  $V_{fe} = 0$ .

- C) What is de-sensitivity in feedback amplifiers? How it affects the characteristics of amplifiers? (2)

- 5) Define and explain Barkhausen criteria. (2)

A)

B) Modify the following amplifier circuit in to a sinusoidal oscillator to produce sustained oscillations of frequency 5 KHz. Also determine the value of  $R_C$  required. Assume  $r_0 = \infty$  and Silicon transistor.

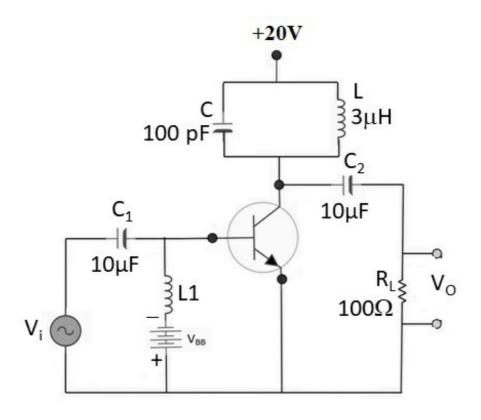

- C) For the power amplifier shown below, the operating frequency is 3MHz and  $V_{CE(Sat)} = 0.3V$ . (4) Determine:

- i. A.C power output

- ii. D.C power drawn by the circuit

- iii. Efficiency, and

- iv. Conduction angle, if peak current is 500 mA

-----End-----