## **Question Paper**

Exam Date & Time: 22-May-2023 (02:30 PM - 05:30 PM)

## MANIPAL ACADEMY OF HIGHER EDUCATION

## FOURTH SEMESTER B.TECH. (ELECTRONICS AND COMMUNICATION ENGINEERING) EXAMINATIONS - MAY/JUNE 2023

SUBJECT: ECE 2253/ ECE 2253 - LINEAR INTEGRATED CIRCUITS

Marks: 50 Duration: 180 mins.

## Answer all the questions.

Missing data may be suitably assumed. Assume Opamp saturation voltage to be  $\pm 12V$ .

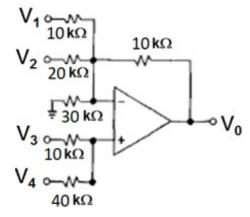

Obtain expression for output voltage of the circuit shown below. Also if  $V_1$  is varied from 0 to 10 V, (5) keeping  $V_2$ ,  $V_3$ ,  $V_4$  at 1V, sketch output voltage with respect to input voltage.

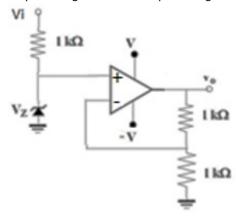

1B) In the Circuit shown in figure, an ideal Zener diode with breakdown voltage of 4.7V is used. Plot the (3) output voltage verses the input voltage. Input voltage varies from 0 to 15 V.

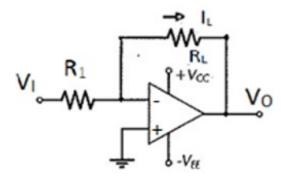

1C) Circuit shown below is voltage to current converter. Given  $V_1 = 2 V$ ,  $R_1 = 1 k\Omega$  maximum output (2) current through the op-amp is  $\pm 10$  mA. Determine (i)  $I_L$  (ii) Maximum value of  $R_L$  that can be used. (iii) Maximum value of  $V_1$  that can be used, given  $R_1 = 1 k\Omega$  and  $R_L = 0$ .

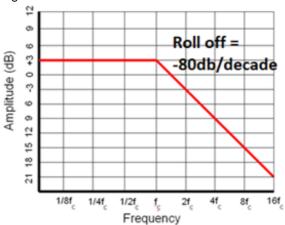

Design a Butterworth LPF with cut-off frequency,  $f_c = 1 \text{kHz}$  for the frequency response shown in Fig. Q2A.

Fig. Q2A

2C)

2B) Analyse the temperature compensated logarithmic amplifier with a neat diagram and obtain the output expression. (3)

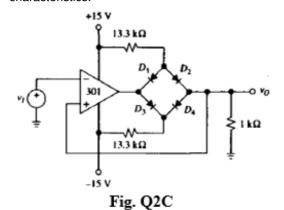

For the circuit shown in Fig. Q2C. given a silicon diode, and  $V_{Sat} = \pm 13V$ . Draw the transfer characteristics. (2)

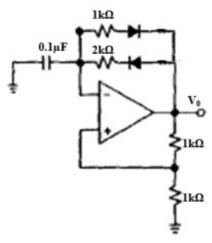

3A) i) By marking all the voltage levels and time intervals, plot  $V_0$  as a function of time for the circuit (5) shown in figure.

ii) What would be the effect on waveform, if  $2k\Omega$  resistor is replaced by a  $1k\Omega$  fixed resistor in series with a  $1k\Omega$  potentiometer and the latter is varied from minimum to maximum value.

- 3B) Design a 555 timer based circuit to give a square waveform of 1kHz frequency and duty cycle (3) adjustable between 25% to 75%.

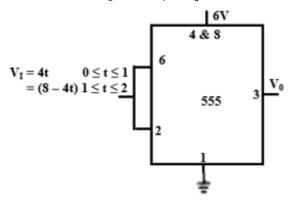

- 3C) For the circuit of shown, if  $V_I$  is a triangular waveform defined as in figure, by marking all the time (2) intervals and voltage levels, plot  $V_0$  as a function of time.

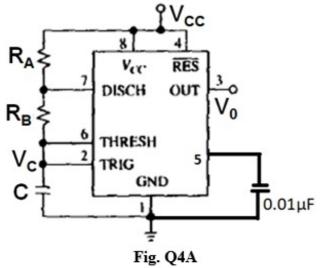

Design a a stable multivibrator shown in Fig. Q4A having with frequency 1 KHz. Assume C =  $0.1\mu$ F, (5) also find the duty cycle D.

- 4B) Draw the internal diagram of VCO and explain its working.

- 4C) With a neat block diagram explain the working of frequency multiplier using PLL. (2)

- 5A) Design a 4-bit R 2R DAC to result in an output voltage of 0.5V when the input is 0001. Use  $V_{REF}$  (5) of -5V and resistor connected to output terminal of  $1k\Omega$  value. What would be the output voltage when the input is 1111. Plot  $V_0$  if the input is coming from a 4-bit Johnson counter driven with a 1kHz clock signal.

- 5B) Explain the working principle of a SAR ADC with an example. (3)

- 5C) In a 4 bit ADC, if the clock frequency is 1kHz, determine the minimum and maximum conversion (2)

(3)

| time, if the ADC is (i) counter type (ii) successive approximation type. |  |

|--------------------------------------------------------------------------|--|

| End                                                                      |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |

|                                                                          |  |