## **Question Paper**

Exam Date & Time: 22-May-2023 (10:00 AM - 01:00 PM)

## MANIPAL ACADEMY OF HIGHER EDUCATION

Manipal School of Information Sciences (MSIS), Manipal Second Semester Master of Engineering - ME (VLSI Design) Degree Examination - May 2023

Physical Design Elective -2 [VLS 5234]

Marks: 100 Duration: 180 mins.

## Monday, May 22, 2023

## Answer all the questions.

- List and explain the properties of static CMOS and dynamic CMOS logic (10) gates

- Describe any three layout design rules and implement the function f=! (10) (ab+cd) in static CMOS logic and draw the stick diagram for the same

- List the data required for floorplan. Explain the technology and library files with suitable examples.

- Explain IO pad placement and power planning in physical design step (10)

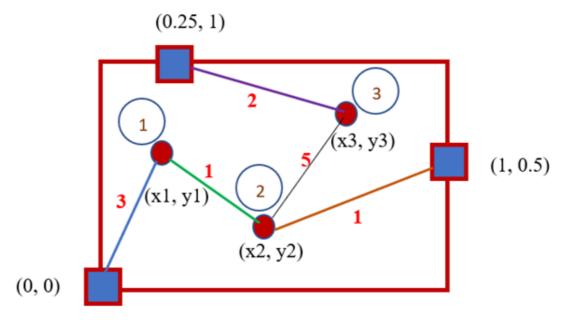

- Compute and draw the locations of gates 1, 2, and 3 shown below using (10) quadratic analytical placement

- <sup>6)</sup> Apply and explain maze routing steps of global routing with multi targets <sup>(10)</sup>

- and multi metal layers with examples

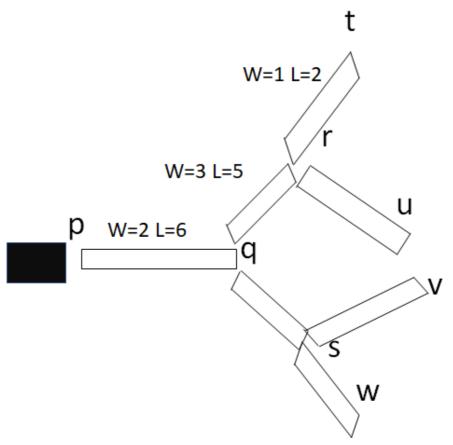

- Calculate delay at output nodes t and v. Assume a capacitance of 2 units at each output.

- Consider R-r\*I /W and C-c\*W\*I assume r-1.5 and c-3

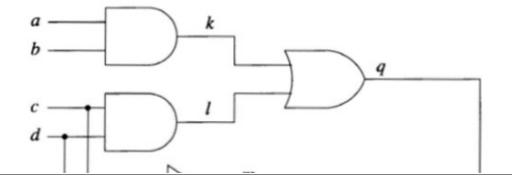

- 8) Compute the collapse ratio for a carry circuit of a 1-bit full adder gate (10) level circuit.

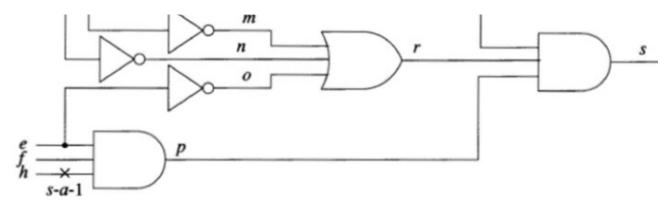

- 9) Identify and explain the test vector for s-a-1 fault at h

Define Built in Self Testing (BIST). How a pseudo random pattern can be generated using linear feedback shift registers. Explain with the help of an example.

----End-----