# **Question Paper**

Exam Date & Time: 07-Dec-2023 (09:30 AM - 12:30 PM)

# MANIPAL ACADEMY OF HIGHER EDUCATION

## THIRD SEMESTER B.TECH. DEGREE EXAMINATIONS - NOVEMBER / DECEMBER 2023 SUBJECT: CSE 2123- DIGITAL SYSTEM DESIGN

Marks: 50

Duration: 180 mins.

### Answer all the questions.

#### Missing data may be suitably assumed.

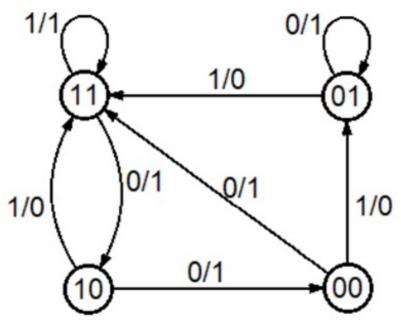

1A)

For the following state diagram, derive the expressions required for the synchronous sequential (5) circuit design using JK flip-flops.

- 1B) Make use of functional decomposition to find the minimum-cost circuit for the function *f* (*x*1, *x*2, *x*3, (3) *x*4) = ∑*m*(4, 7, 9, 10, 12, 13, 14, 15). Assume that the input variables are available in uncomplemented form only.

1C) Demonstrate SR latch (basic Flip Flop circuit) using NAND gates with its function table. (2)

- 2A) It is required to develop a system to swap the contents of two n-bit registers. Assume that a (5) temporary register is available to assist swapping. Adopt state table approach to design control circuit. Control circuit has two inputs clock and w. The swapping process is initiated when w=1, and on completion the control circuit asserts a signal Done to 1.

i) Derive the expression for the outputs of control circuit.

ii) Develop bus architecture of the system based on tri-state buffer.

- A combinational circuit receives two single-bit inputs A and B and produces a single-bit output Y = (3) F1|F2. The Boolean functions F1 and F2 are as given below and are implemented using a decoder and OR gates. Design a minimal circuit for Y using only one decoder, one 2:1 multiplexer, and OR gates.

$F1(A, B) = \sum m (2, 3)$

$F2(A, B) = \sum m (0,1,3)$

- Construct JK Flip Flop from D Flip Flop 2C)

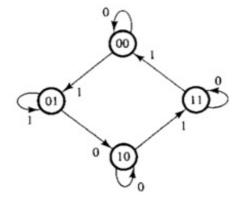

- Design the synchronous counter with the following repeated binary sequence: 0, 1, 2, 4, 6. Use D 3A) (5) flip-flops. Check if it is self-correcting or not.

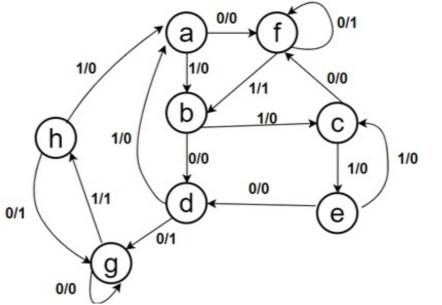

- Analyze the following state diagram and perform the state reduction. 3B)

- Distinguish between Moore and Mealy models of sequential circuit design. 3C) (2)

- Since a computer has many registers, paths must be provided to transfer information from one (5) 4A) register to another. An efficient scheme for transferring the information between registers in a multiple-register configuration is a common bus system. Design a 4-bit common bus system for 4registers of 4-bits each using multiplexers.

Design 3-bit Johnson counter by implementing the following steps. 4B) (3)a) Draw the state-transition diagram.

- b) Construct state table using T flip-flops.

- c) Design the Counter.

- 4C) Design NAND gate using CMOS technology.

- 5A) Draw the state table and design the synchronous sequential circuit for the following state diagram (4) using JK FF:

| 5B) | Design a combinational unit that can act as adder and subtractor for two 4-bit numbers. Provide suitable explanation. | (4) |

|-----|-----------------------------------------------------------------------------------------------------------------------|-----|

| 5C) | Design a 4-bit ring counter using D flip-flops.                                                                       | (2) |

(2)

(2)

(2)

(3)

-----End-----