# **Question Paper**

Exam Date & Time: 05-Dec-2023 (09:30 AM - 12:30 PM)

# MANIPAL ACADEMY OF HIGHER EDUCATION

#### THIRD SEMESTER B.TECH. DEGREE EXAMINATIONS - NOVEMBER / DECEMBER 2023 SUBJECT: ECE 2121- ANALOG ELECTRONIC CIRCUITS

Marks: 50

Duration: 180 mins.

#### Answer all the questions.

#### Missing data may be suitably assumed.

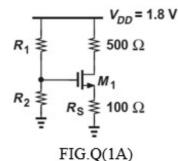

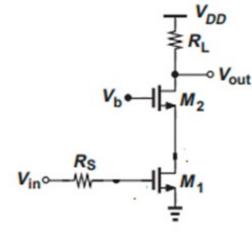

1A)

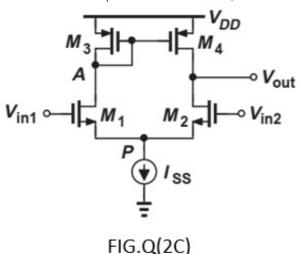

The circuit shown in FIG.Q(1A) must be designed for a voltage drop of 200 mV across R<sub>S</sub>. Assume (4)  $\mu_n C_{ox} = 200 \mu A/V^2$  and  $V_{TH} = 0.4V$ .

i) Calculate the minimum allowable value of (W/L ) if 'M1' must remain in saturation.

ii) What are the required values of 'R1' and 'R2' for an input impedance of at least 30 K\Omega?

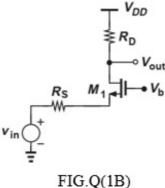

1B)

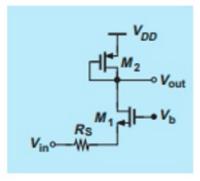

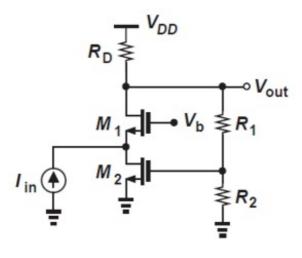

Draw the small signal model and determine the input impedance of the circuit shown in FIG.Q(1B). (3) Assume  $\lambda = 0$ .

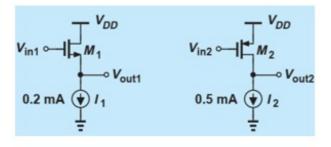

1C)

An integrated circuit employs the source follower and the common-source stage as shown in (3) FIG.Q(1C). Design a current mirror that produces  $I_1$  and  $I_2$  from a 0.3 mA reference.

#### FIG.Q(1C)

2A) Design an amplifier to drive a 50 $\Omega$  load with a voltage gain of 0.5 and a power budget of 10 mW. (4) Assume  $\mu_n C_{\alpha x} = 100 \ \mu A/V^2$ ,  $V_{TH} = 0.5 \ V$ ,  $\lambda = 0$  and  $V_{DD} = 1.8 \ V$ .

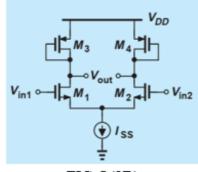

Assuming  $\lambda \neq 0$ , compute the single-ended differential and common mode voltage gains for the (3) circuit shown in FIG.Q(2B) using half circuit analysis.

#### FIG.Q(2B)

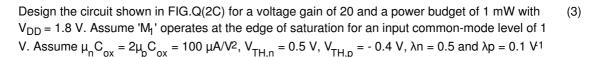

2C)

2B)

3A)

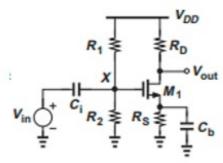

For the circuit shown in FIG.Q(3A), find the input and output poles at high frequencies for  $\lambda \neq 0$ . (4) Sketch the frequency response.

## FIG.Q3(A)

3B)

For the circuit shown in FIG.Q3(B), find the poles at low frequencies. Also, sketch its low frequency (3) response. Assume  $\lambda = 0$ .

3C)

For the circuit shown in FIG.Q(3C), find the pole frequencies and sketch the frequency response. (3)

## FIG.Q(3C)

4A)

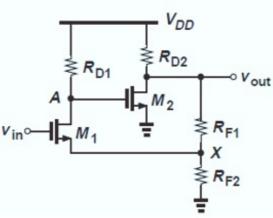

Determine the closed-loop gain, I/O impedance of the circuit shown in FIG. Q(4A), assuming R1 + (4) R2 is very large &  $\lambda=0$ .

FIG. Q(4A)

4B)

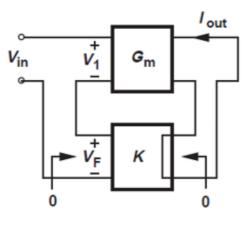

For the block diagram shown in FIG. Q(4B), identify the feedback topology and obtain the expressions for input and output impedance.

(3)

FIG. Q(4B)

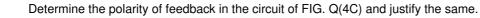

4C)

(3)

## FIG. Q(4C)

5A) Explain the working principle of RC phase shift Oscillator with a neat circuit diagram. Obtain the (4) expressions for minimum gain and frequency of oscillation. Also, find the frequency of oscillation for  $R=1K\Omega$  and  $C=1\mu F$ .

5B) Explain the working principle of ring oscillator with a neat circuit diagram. Obtain the expressions for (3) minimum gain and frequency of oscillation. Also, find the frequency of oscillation for drain resistance and capacitance of 1KΩ and 1µF.

-----End-----