## II SEMESTER M. TECH (EMBEDDED CONTROL AND AUTOMATION) END SEMESTER EXAMINATIONS MAY 2024 VLSI SYSTEM DESIGN (ICE 5412)

| Time:3 Hours 09-05 -2024 |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IAX. N | IARK | S: 50 |    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------|----|

|                          | Instructions to Candidates:                                                                                                                                                                                                                                                                                                                                                                                                                      |        |      |       |    |

|                          | <ul> <li>Answer ALL the questions.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |        |      |       |    |

| Q.No.                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      | М      | со   | PO'S  | BL |

| 1A                       | Differentiate between enhancement mode and depletion mode transistors.                                                                                                                                                                                                                                                                                                                                                                           | 3      | 1    | 5     | 4  |

| 1B                       | An nFET with L=0.5 $\mu$ m is built in a process where the process transconductance is 100 $\mu$ <i>A</i> / <i>V</i> <sup>2</sup> and <i>V</i> <sub><i>Tn</i></sub> = 0.7 <i>V</i> . The gate source voltage is set to a value of <i>V</i> <sub><i>Gsn</i></sub> = <i>V</i> <sub><i>DD</i></sub> = 3.3 <i>V</i> . Calculate the required channel width 'W' to obtain a resistance <i>R</i> <sub><i>n</i></sub> = 950 $\Omega$ .                  | 3      | 1    | 4     | 3  |

| 1C                       | Calculate the total capacitance $C_{out}$ of the NOT gate shown in figure 1C with a load capacitance $C_L = 120 \ FF$ .                                                                                                                                                                                                                                                                                                                          | 4      | 2    | 4     | 3  |

|                          | VDD<br>VDD<br>k = pFET drain<br>$k = 1 \mu m (drawn)$<br>$L = 1 \mu m (drawn)$<br>$L_o = 0.1 \mu m$<br>$V_{DD} = 5 V$<br>$C_{ox} = 2.70 \text{ fF}/\mu m^2$<br>$mFET: k_p = 60 \mu A/v^2$<br>$C_j = 1.05 \text{ fF}/\mu m^2$<br>$C_{jsu} = 0.32 \text{ fF}/\mu m^2$<br>$V_{DD} = 0.1 \mu m$<br>$V_{DD} = 5 V$<br>$C_{ox} = 2.70 \text{ fF}/\mu m^2$<br>$V_{TOR} = 0.6 V$<br>$C_j = 0.86 \text{ fF}/\mu m^2$<br>$C_{jsw} = 0.24 \text{ fF}/\mu m$ |        |      |       |    |

|                          | Figure 1C                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |      |       |    |

| 2A                       | A CMOS logic gate that implements the function:                                                                                                                                                                                                                                                                                                                                                                                                  | 4      | 2    | 4     | 5  |

|                          | $f = \overline{(a+b).(b+c).d}$                                                                                                                                                                                                                                                                                                                                                                                                                   |        |      |       |    |

|                          | is needed in a control network. Design the logic circuit with device sizes in the gate that equalize the nFET and pFET resistances. Identify the worst-case nFET and pFET paths that will slow down the response.                                                                                                                                                                                                                                |        |      |       |    |

| 2B                       | With equations, illustrate how device parameters (any six) of a MOSFET are scaled using the constant voltage scaling model.                                                                                                                                                                                                                                                                                                                      | 3      | 2    | 5     | 3  |

| 2C                       | Compare and contrast the working of pass transistors and transmission gates.                                                                                                                                                                                                                                                                                                                                                                     | 3      | 2    | 4     | 4  |

| 3A                       | Sketch the transistor-level schematic and stick diagram for implementing the following function: $f = \overline{a.b.c + a.d}$                                                                                                                                                                                                                                                                                                                    | 3      | 3    | 4     | 3  |

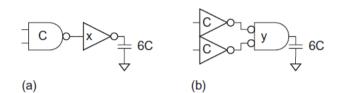

3B Consider the two designs of a 2-input AND gate shown in Figure 3B

(a) and (b). Justify which of the two circuits will be faster with a calculation of the path effort, delay, and input capacitances x and y to achieve this delay.

Figure 3B

**3C** Sketch a transistor level schematic of a pseudo-nMOS gate that **3 3 4 3** implements the function:

$$F = \overline{A(B + C + D) + E.F.G}$$

- **4A** Sketch the transistor level schematic of a clocked JK latch.

- **4B** Implement the following state table using a ROM and two D flip-flops **3** where 'X' is the input and 'Z' is the output and  $S_0, S_1, S_2$  and  $S_3$  are the states:

| Present State         | Next State            |                       | Outp | out (Z) |

|-----------------------|-----------------------|-----------------------|------|---------|

|                       | X=0                   | X=1                   | X=0  | X=1     |

| S <sub>0</sub>        | <i>S</i> <sub>0</sub> | <i>S</i> <sub>1</sub> | 0    | 1       |

| <i>S</i> <sub>1</sub> | <i>S</i> <sub>2</sub> | S <sub>3</sub>        | 1    | 0       |

| <i>S</i> <sub>2</sub> | <i>S</i> <sub>1</sub> | S <sub>3</sub>        | 1    | 0       |

| <i>S</i> <sub>3</sub> | <i>S</i> <sub>3</sub> | <i>S</i> <sub>2</sub> | 0    | 1       |

Draw the block diagram and the ROM truth table.

| 4C | Illustrate different programming technologies of an FPGA with figures.                                        | 4 | 4 | 5 | 3 |

|----|---------------------------------------------------------------------------------------------------------------|---|---|---|---|

| 5A | With a flowchart, illustrate the design flow starting from the specification of a chip to its implementation. | 4 | 4 | 5 | 3 |

| 5B | Compare the three main approaches followed in design for testability in VLSI systems.                         | 3 | 5 | 5 | 4 |

| 5C | Interpret the different types of IC packaging techniques that are available in VLSI systems.                  | 3 | 5 | 5 | 3 |